文章来源:高电压技术

作者:汪 涛,黄樟坚,虞晓阳,张茂强,骆仁松,李 响(南京南瑞继保电气有限公司,南京 211102)

摘 要:碳化硅(SiC)MOSFETs 短路承受能力弱,研究其短路保护方法成为保障电力电子设备安全运行的重要课题。现有方法大多围绕低压小功率 SiC MOSFETs,然而随着电压和功率等级的提升,器件特性有所差异,直接套用以往设计难以实现高压大功率 SiC MOSFETs 的快速、可靠保护。该文首先详细研究了几种常用短路检测方法;其次基于高压大功率 SiC MOSFETs 器件特性,深入对比分析了不同短路检测方法的适用性,提出一种阻容式漏源极电压检测和栅极电荷检测相结合的短路保护方法;最后搭建了实验平台验证所提方法的可行性。结果表明,提出的方法在硬开关短路故障(hard switching fault,HSF)下,保护响应时间缩短了 1.4 μs,短路能量降低了 62.5 %;且能可靠识别负载短路故障(fault under load,FUL)。

关键词:SiC MOSFETs;高压大功率;短路保护;器件特性;漏源极电压;栅极电荷

0 引言1

近年 来 , 知 名 半 导 体 器 件 厂 家 陆 续 推 出 了3.3 kV 高压 大 功 率 碳 化 硅 (silicon carbide , SiC MOSFETs 模块[1-2]。随着电压和功率等级提升,SiC MOSFET 在简化拓扑结构、减少器件数量、提高功率密度等方面更具优势,已成为新能源发电、机车牵引等领域的关注热点[3-6]。由于 SiC MOSFET 芯片面积小、电流密度高,导致其短路承受能力弱,研究 SiC MOSFET 的短路保护电路对确保电力电子设备安全运行尤为重要。

目前,已有一些文献对 SiC MOSFET 的短路检测方法开展研究,主要分为 3 类。

第 1 类是漏源极电压检测法[7-11],通过检测正常开通和短路故障下的漏源极电压差异,实现器件的短路保护,该方法能可靠识别硬开关短路故障(hard switching fault,HSF)和负载短路故障(fault under load,FUL),已广泛用于商业驱动中,但此方法需设置消隐时间 tblk,避免正常开通过程保护误动,导致保护响应速度减慢。

第 2 类是电流或电流变化率检测法[12-24],通过检测器件漏极电流 id 判断是否发生短路故障,常见的有分流器检测法[12]、电流镜像检测法[13]、罗氏线圈检测法[14-15]和寄生电感检测法[16-18]。分流器检测法通常在功率回路引入同轴分流器等线性元件来进行短路保护,但随着功率回路电流的增大,分流器带来的损耗及成本不可忽视;电流镜像检测法要求器件内部集成电流镜像功能,不具有普适性;罗氏线圈电流检测法信号处理电路设计复杂,在实际工程中难以推广应用;寄生电感检测法采用器件开尔文源极与功率源极间的寄生电感来检测漏极电流,该方法电路简单,且无需设置消隐时间,保护响应快速,但该方法受寄生电感、漏极电流变化率等因素影响。

第 3 类是栅极电荷检测法[19-22],当发生 HSF短路时,米勒平台消失,栅极充电电荷减小,通过检测正常开通与故障状态下栅极充电电荷差异判断是否发生 HSF 短路,该方法也无需设置消隐时间,保护响应快速,但受器件电容特性影响较大,且难以识别 FUL 短路。

综上所述,现有短路检测方法存在响应速度慢、受器件特性影响大或 FUL 故障识别困难等问题;且大多围绕 1.2 kV 以下的低压小功率 SiC MOSFETs,鲜有针对高压大功率 SiC MOSFETs 短路保护开展详细研究[23-24]。然而随着电压、电流等级提升,相比低压小功率 SiC MOSFETs,高压大功率 SiC MOSFETs 在器件特性方面存在明显差异:

1)高压大功率 SiC MOSFETs 输入电容 Ciss 增大,器件开通过程减慢。

2)高压大功率 SiC MOSFETs 输入电容 Ciss 增大,开通瞬间的漏极电流变化率降低。

3)高压大功率 SiC MOSFETs 转移电容 Crss 增加,正常开通及 HSF 故障下的栅极充电电荷特性差异更大。

若简单套用以往低压小功率 SiC MOSFETs 的短路保护设计,会影响高压大功率 SiC MOSFETs短路 保 护 的 快 速 性 和 可 靠 性 。因 此 , 该 文 从3.3 kV/750 A 高压大功率 SiC MOSFET 的器件特性出发,深入对比分析了几种常用短路检测方法的适用性,提出一种阻容式漏源极电压检测与栅极电荷检测相结合的高压大功率 SiC MOSFETs 短路保护方法,既实现了 HSF 和 FUL 故障的可靠识别,又兼顾了保护响应的快速性,并搭建了实验平台对所提方法的短路保护效果进行验证。

1 SiC MOSFET 短路检测方法

1.1 SiC MOSFET 短路分类

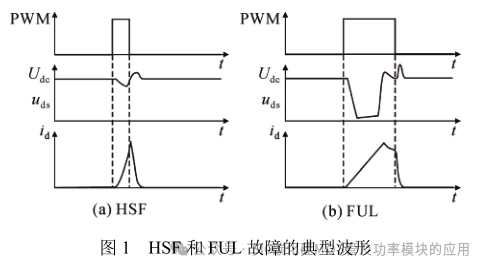

SiC MOSFET 短路故障分为 HSF 和 FUL 两类,典型波形如图 1 所示。HSF 短路回路电感小,如桥臂直通,开通瞬间 id 快速上升,SiC MOSFET 退出电流线性区,进入电流饱和区,漏源极电压 uds 抬升至母线电压 Udc;FUL 是负载短路引起的故障,如相间短路等,短路回路电感更大,开通瞬间 id 上升更慢,uds 先降至通态压降,当 id 上升到一定值时,SiC MOSFET 才开始退出电流线性区,此时 uds 再迅速抬升至 Udc。

短路保护的关键是故障检测,该章节详细研究了漏源极电压检测法、寄生电感检测法和栅极电荷检测 法 , 并 基 于 3.3 kV/750 A 高压 大 功 率 SiC MOSFET 模块[1],从器件特性出发,深入对比分析了 3 种不同检测方法的适用性。

1.2 漏源极电压检测法

漏源 极 电 压 检 测 法 的 基 本 原 理 为 :SiC MOSFET 正常导通时 uds 为通态压降,发生短路故障时 uds 抬升至 Udc,通过检测正常开通和短路故障下的 uds 差异,即可识别 HSF 和 FUL 短路故障。根据检测电路不同,可分为二极管式[7]和阻容式[9]。

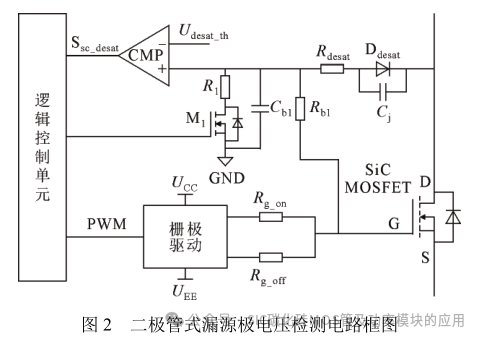

图 2 为常用二极管式漏源极电压检测电路。当SiC MOSFET 开通发生短路故障,uds 抬升,二极管Ddesat 截止,栅极驱动输出的驱动正压 UCC 经 Rbl 给Cbl 充电,当 Cbl 两端电压 uCbl 大于比较器阈值电压Udesat_th,比较器输出高电平故障检测信号 Ssc_desat;SiC MOSFET 关断时,栅极驱动输出驱动负压 UEE,开关管 M1 导通,Cbl 经 R1 快速放电,检测电路被闭锁;此外,关断瞬间快速变化的 duds/dt 经 Ddesat 结电容 Cj 给 Cbl 充电,可能造成检测电路误触发,因此在 Ddesat 支路串接阻尼电阻 Rdesat 抑制干扰。

SiC MOSFET 正常开通,随着 uds 降低,Ddesat从阻 态 转 换 为 通 态 , 当 器 件 完 全 导 通 时 ,uCbl<Udesat_th,uCbl 表达式为:

式(1)中:Uds_on 为 SiC MOSFET 导通压降;UF 为Ddesat 正向导通压降。

二极管式漏源极电压检测已广泛应用于低压小功 率 器 件 短 路 保 护 。 然 而 高 压 大 功 率 SiC MOSFETs 的 Uds_on 较高,且随着温度升高、通态电流增加 Uds_on 进一步增大;加之更高母线电压需更多二极管串联来提高 Ddesat 阻断电压,使得 UF 也增大;由式(1)可知,Uds_on 和 UF 增大导致 uCbl 随之升高,使 uCbl 很可能触及 Udesat_th,引起检测电路误触发。因此,高压大功率器件短路保护大都采用可靠性更高的阻容式漏源极电压检测电路。

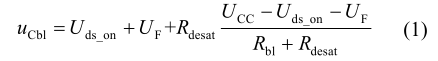

图 3 为常用阻容式漏源极电压检测电路。SiCMOSFET 关断时,开关管 M1 导通,Cbl 经 R1 完全放电,检测电路被闭锁,此时 Rdesat 和 Cdesat 承受母线电压,Rdesat 阻值通常达到兆欧级,以使 Rdesat 功率满足要求。当 SiC MOSFET 开通发生短路故障,uds 抬升,并经 Rdesat 给 Cbl 充电,当 uCbl>Udesat_th 时,比较器输出高电平故障检测信号 Ssc_desat,采用钳位二极管 Dc_1 和 Dc_2 防止 uCbl 超出比较器允许输入电压范围。由于 Rdesat 和 Rbl 阻值很大,Cbl 并联的寄生电容 Cp 不可忽略,Cp 包括 Dc_2 结电容、比较器输入电容等,且 Cp 容值随元器件选型不同有所差异,从数皮法至数十皮法不等,由于 Cp 容值测量困难,在实际工程应用中,通常根据实验结果调节 Cbl,从而获得期望的检测响应时间。若短路故障为 FUL,则 uds 先降至通态压降后再抬升至 Udc,快速变化的duds/dt 通过 Cdesat 支路能加快 Cbl 充电速度,从而缩短检测响应时间。

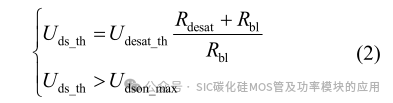

为了 避 免 SiC MOSFET 完全 导 通 之 后uCbl>Udesat_th,引起保护误触发,Rdesat 和 Rbl 的取值应满足表达式:

式中:Udson_max 为各工况条件下 SiC MOSFET 导通压降最大值;Uds_th 为可将 Cbl 充电至 Udesat_th 的 uds阈值电压。在实际工程应用中,Udson_max 一般选择1.5~2 倍额定电流[7],最高工作结温下的导通压降。

以该文 3.3 kV/750 A SiC MOSFET 为例,在 2 倍额定电流,最高工作结温下 Uds_on 约 7.8 V,因此Uds_th>7.8 V。若 Uds_th 设置留有足够安全裕量,便可避免 SiC MOSFET 在完全导通之后保护误触发。

此外,为了避免器件在完全导通之前,uCbl 被uds 充电至 Udesat_th,引起保护误触发,需预留足够的tblk。定义 ton_desat 为 ugs 开始上升到 uds 下降至通态压降的开通时间,则 tblk 需满足[7,25]:

式中:ton_max 为各工况条件下 ton_desat 的最大值。

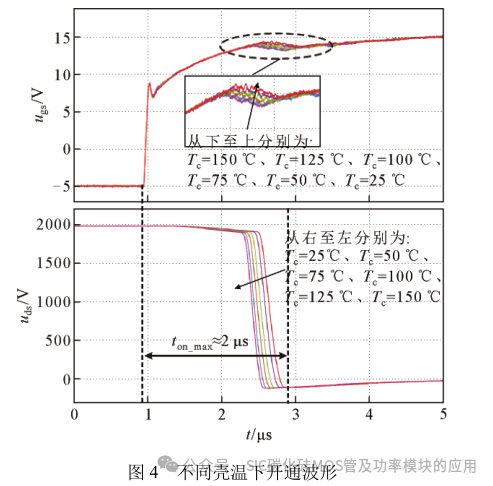

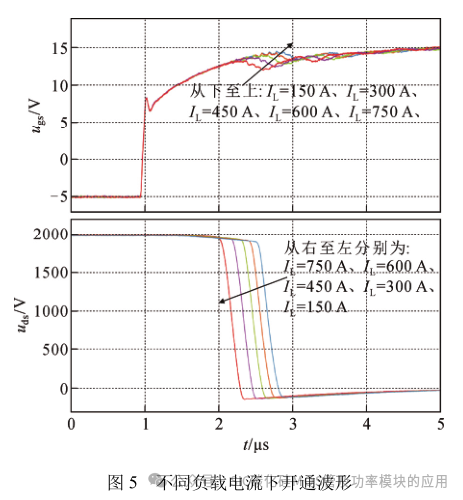

图 4 给出了母线电压 Udc=2 kV,负载电流IL=750 A,壳温 Tc 分别为 25、50、75、100、125、150 ℃时 SiC MOSFET 的开通实验波形。

图 5 给出了母线电压 Udc=2 kV,壳温 Tc=25 ℃,负载电流 IL 分别为 150、300、450、500、750 A 时SiC MOSFET 的开通实验波形。

由图 4、图 5 的实验结果分析可知,温度越低、负载电流越大,ton_desat 越长。以 3.3 kV/750 A SiC MOSFET 为例,ton_max≈2 μs,代入式(3)得 tblk>2.4 μs,因此,该文取 tblk=2.5 μs。

现有阻容式 uds 检测电路大多通过调整 Cbl 充电时间常数来设置 tblk,该方法易受 uds 和检测电路寄生参数影响,tblk 调节不方便且精度较差。因此,该文通过逻辑控制单元来设置 tblk,在 tblk 内,逻辑控制单元屏蔽 Ssc_desat,在 tblk 结束后,才开始检测高电平故障信号 Ssc_desat,数字化的配置方式有效提高了 tblk 调节的灵活性和精确度。

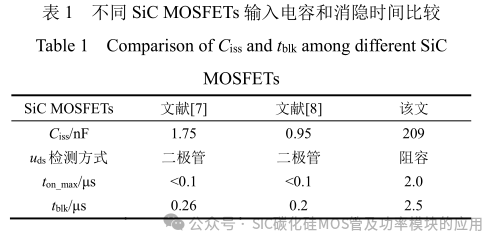

表 1 比较了文献[7]的 900 V/63 A、文献[8]的1.2 kV/40 A 和该文 3.3 kV/750 A 3 种 SiC MOSFETs的输入电容和采用 uds 检测电路识别 HSF 故障的消隐时间。

从对比结果可知,低压小功率 SiC MOSFETs输入电容小,开通过程快,消隐时间短,使用 uds检测即可实现 HSF 故障的快速保护;而高压大功率SiC MOSFETs 输入电容大幅提高,开通过程明显减慢,消隐时间成倍增加,极大降低了 HSF 故障的保护响应速度。

1.3 寄生电感检测法

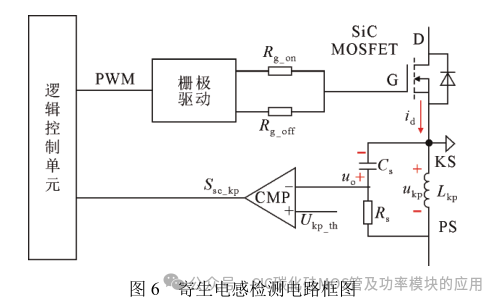

寄生电感检测法基本原理为:功率器件开尔文源极(Kelvin source,KS)与功率源极(power source,PS)之间存在寄生电感 Lkp,快速变化的 id 在 Lkp 两端感应出电压 ukp,通过对 ukp 积分,即可得到与 id幅值成比例的输出电压 uo 幅值,并以此识别短路故障。寄生电感检测法无需设置消隐时间,保护响应速度快于漏源极电压检测。典型的寄生电感检测电路框图如图 6 所示。

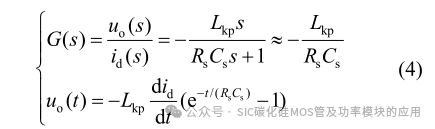

图 6 中,为了避免检测电路影响器件正常工作,Rs 和 Cs 支路阻抗应远大于 Lkp 阻抗,使 id 几乎不流入检测电路。uo 与 id 的传递函数与时域表达式如式(4)所示。

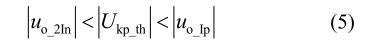

由式(4)可知,若漏极电流变化率 did/dt 足够大,即 id 等效频率足够高时,RsCss>>1,此时 uo 与 id 的传递函数近似为常数,uo 幅值与 id 幅值呈线性关系。当 uo 幅值大于阈值电压 Ukp_th 幅值,比较器输出高电平故障检测信号 Ssc_kp。在实际工程应用中,为避免正常开通过程保护误动或发生短路故障时保护拒动,Ukp_th 需满足[16]:

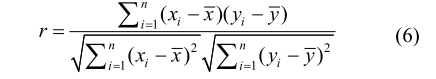

式中:|Ukp_th|为 Ukp_th 幅值;|uo_2In|为 2 倍额定电流开通对应的 uo 幅值;|uo_Ip|为短路故障峰值电流对应的 uo 幅值。为便于评估 uo 与 id 的线性度,引入相关系数 r,r 表达式为:

式中:变量 x 代入 uo;变量 y 代入 id;则可得到 uo与 id 的相关系数 r。r 越趋近于 1,表示 uo 与 id 的线性度越高。

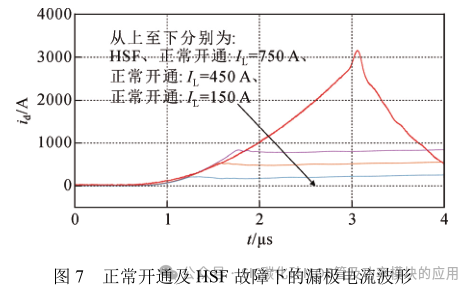

从式(4)所示时域表达式可知,uo 由 Lkp、did/dt和时间常数 τ=RsCs 决定。Lkp 可根据文献[18]所述测试方法或查阅器件数据手册获得,该文 3.3 kV/750A SiC MOSFET 寄生电感 Lkp 约 5 nH[26]。图 7 给出了Udc=2 kV,Tc=25 ℃时,正常开通及 HSF 故障下的id 波形。由图 7 可知,正常开通与 HSF 故障 did/dt差别不大,did/dt≈1.25 kA/μs。

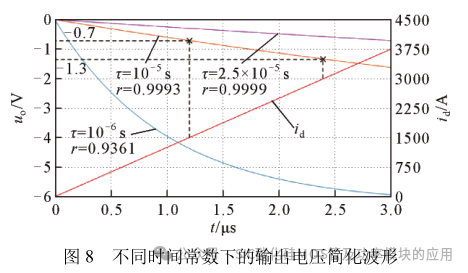

为了便于分析,假设 HSF 故障 id 保持恒定电流变化率 1.25 kA/μs 线性增大。图 8 给出了 HSF 故障下 id 经简化处理,且 Lkp=5 nH,不同 τ 下的 uo 波形。

由图 8 可知,τ 越大,r 越趋近于 1,uo 与 id 线性度越高,但 uo 幅值也越小。由图 7 可知,Udc=2 kV,Tc=25 ℃,该文 3.3 kV/750 A SiC MOSFET 短路故障id 峰值 约 3 kA ,结 合 式 (5) 和图 8 可得 , 当τ=2.5×10−5 s,r=0.9999 时,uo 与 id 呈线性关系,Ukp_th设置范围为−0.6~−0.3 V,Ukp_th 幅值和设置范围都太小;当 τ=10−5 s,r=0.9993 时,uo 与 id 仍近似呈线性关系,Ukp_th 设置范围扩大至−1.3~−0.7 V,但 Ukp_th幅值和设置范围仍偏小;当 τ=10−6 s,r=0.9361 时,uo 与 id 虽然呈正相关,但 uo 与 id 线性度变差,uo幅值已不能较为准确地反映 id 幅值。

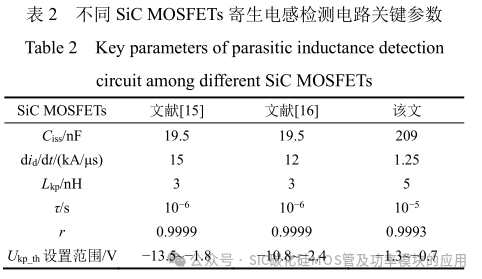

表 2 比较了文献[15]的 1.2 kV/300 A、文献[16]的 1.2 kV/400 A 和该 文 3.3 kV/750 A 3 种 SiC MOSFETs 在 HSF 故障下,采用寄生电感检测电路的关键参数。

从表 2 对比 结 果 可 知 , 高 压 大 功 率 SiC MOSFETs 输入电容 Ciss 大幅增加,HSF 故障下 did/dt也显著变慢,uo 幅值减小,导致 Ukp_th 幅值和设置范围降低,检测电路抗干扰能力变弱,保护容易误动,且随着 Udc 降低,HSF 故障下高压大功率 SiC MOSFETs 的 did/dt 进一步变慢,保护更容易误动。

此外,发生 FUL 故障时 did/dt 上升也会减缓,寄生电感检测法难以可靠识别高压大功率 SiC MOSFETs 的FUL 故障。

1.4 栅极电荷检测法

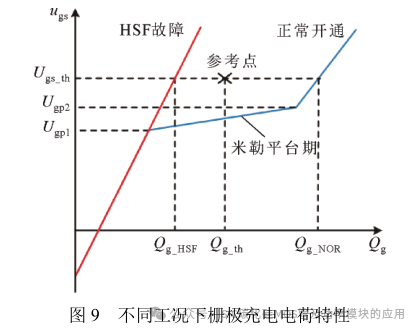

栅极电荷检测的基本原理为:正常开通过程,SiC MOSFET 转移电容 Crss 随 uds 减小而增大,此时栅极电流 ig 绝大部分给 Crss 充电,栅极电压 ugs 缓慢上升进入米勒平台期;而发生 HSF 故障时 SiC MOSFET 退出电流线性区,uds 抬升至 Udc,此时 Crss较小且基本不变,ig 仅极少一部分给 Crss 充电,米勒平台期消失,导致 HSF 故障下栅极充电电荷 Qg相比正常开通过程更小,通过识别 Qg 差异即可实现HSF 故障检测。但发生 FUL 故障时,uds 也先减小至通态压降,此时 Qg 与正常开通过程差异很小,因此该方法难以识别 FUL 故障。

图 9 给出了正常开通过程和 HSF 故障下栅极充电电荷特性曲线。图 9 中米勒平台期 ugs 从 Ugp1 缓慢上升至 Ugp2,Ugs_th 为栅极阈值电压,Qg_th 为栅极阈值电荷,Qg_HSF 为 HSF 故障下 ugs=Ugs_th 的栅极电荷,Qg_NOR 为正常开通 ugs=Ugs_th 的栅极电荷。若满足式(7)所示条件,则可判断 SiC MOSFET发生 HSF 故障。

式中:IL 为负载电流;gm 为器件跨导;Uth 为 SiCMOSFET 开启阈值电压。由于开通过程 gm 呈正温度特性,Uth 呈负温度特性,导致 Ugp 随温度升高而减小;且 Ugp 又随 IL 增大而增加;因此在最低工作温度、最大负载电流工况下 Ugp 最大。从图 4、图 5测试 结 果 可 知 , Ugp_max 约 14.3 V ,驱 动 正 压UCC=17 V ,由 式 (8) 可得 Ugs_th 取值 范 围 为14.3~17 V,该文取 Ugs_th=15 V。

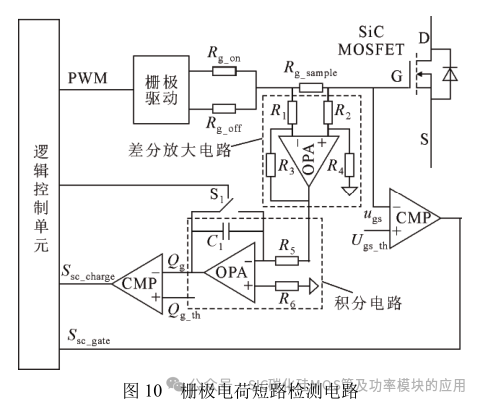

常用栅极电荷检测电路如图 10 所示。开通过程复位开关 S1 断开,使能积分电路,栅极电流 ig由采样电阻 Rg_sample 采集,通过差分放大电路后经积分电路得到 Qg;关断过程 S1 导通,闭锁积分电路,Qg 清零;采用比较器检测 ugs 和 Qg,逻辑控制单元接收比较器输出信号 Ssc_gate 和 Ssc_charge,并根据式(7)判断 SiC MOSFET 是否发生 HSF 故障。

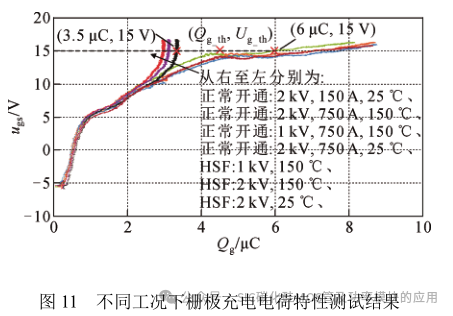

图 11 给出了不同 Udc、不同 Tc 下发生 HSF 故障,以及不同 Udc、不同 IL、不同 Tc 下正常开通,该文 SiC MOSFET 栅极充电电荷特性测试结果。

从图 11 实验结果可知,HSF 故障下 Udc 越低、Tc 越高,ugs=Ugs_th 时 Qg_HSF 越大,栅极电荷短路保护越 容 易 拒 动 , 当 Udc=1 kV , Tc=150 ℃,QHSF_max=3.5 μC;正常开通时 Udc 越高、IL 越大、Tc越低,ugs=Ugs_th 时 Qg_NOR 越小,栅极电荷短路保护越容易误动,当 Udc=2 kV,IL=750 A,Tc=25 ℃,QNOR_min=6 μC。因此,由式(8)可得,当 Ugs_th=15 V时,Qg_th 取值范围为 3.5~6 μC,该文取 Qg_th=4.5 μC。

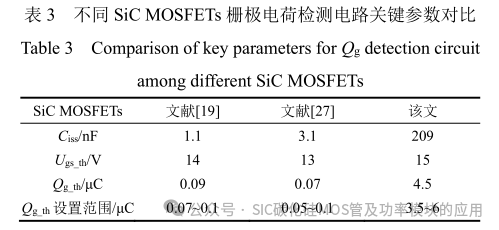

表 3 给出文献[19]的 1.2 kV/24 A、文献[27]的1.2 kV/39 A 和该文 3.3 kV/750 A 的 SiC MOSFET,采用栅极电荷检测电路的关键参数对比。

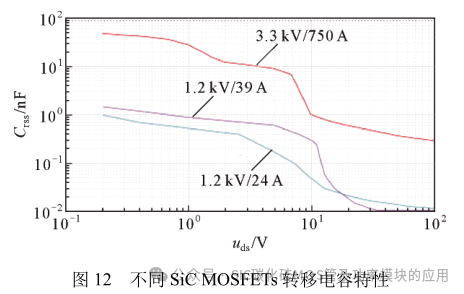

由表 3 可知,高压大功率 SiC MOSFETs 输入电容 Ciss 大幅增加,导致 3.3 kV/750 A SiC MOSFET的 Qg_th 幅值也显著增大,这大大增强了栅极电荷检测电路的抗干扰能力。此外,Qg_th 设置范围也明显变宽,这主要是由于器件 Crss 特性差异所致,表 3中 3 种不同 SiC MOSFETs 转移电容特性曲线如图12 所示。

由图 12 可知,3.3 kV/750 A SiC MOSFET转移电容 Crss 大幅增加,导致其正常开通过程和HSF 故障时的 Qg 差异变大,Qg_th 设置范围也随之变宽,这大大提高了短路保护的可靠性。因此,高压大功率 SiC MOSFETs 采用栅极电荷检测 HSF 故障兼具响应速度快和可靠性高的优点。

2 高压大功率 SiC MOSFETs 短路保护

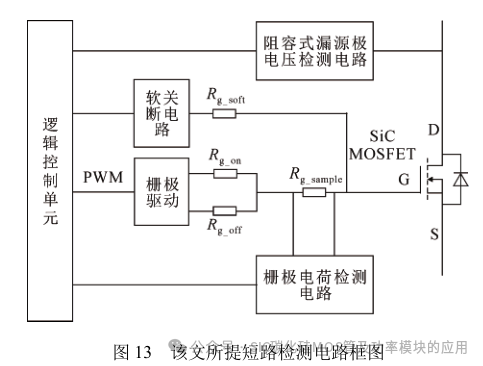

阻容式漏源极电压检测法能可靠识别 HSF 及FUL 故障,但高压大功率 SiC MOSFETs 开通过程变缓,发生 HSF 故障时需设置更长的 tblk 避免保护误动,减慢了保护响应速度;寄生电感检测法虽无需设置 tblk,但高压大功率 SiC MOSFETs 漏极电流变化率降低,导致检测电路 uo 幅值减小,抗干扰能力变弱;栅极电荷检测法也无需设置 tblk,且高压大功率 SiC MOSFETs 转移电容 Crss 增大,HSF 故障与正常开通过程的栅极电荷差异更明显,大幅提高了检测电路工作可靠性,但该方法难以识别 FUL 故障。基于高压大功率 SiC MOSFETs 器件特性和不同短路检测方法自身特点,该文提出一种阻容式漏源极电压检测与栅极电荷检测相结合的高压大功率SiC MOSFETs 短路保护方法,既实现了 HSF 和 FUL故障可靠识别,又兼顾了保护响应快速性,所提方法电路框图如图 13 所示。

图 13 中采用栅极电荷检测电路快速识别 HSF 故障;通过阻容式漏源极电压检测电路识别 FUL 故障;发生短路故障时,经更大阻值 Rg_soft 软关断,防止器件过压损坏。

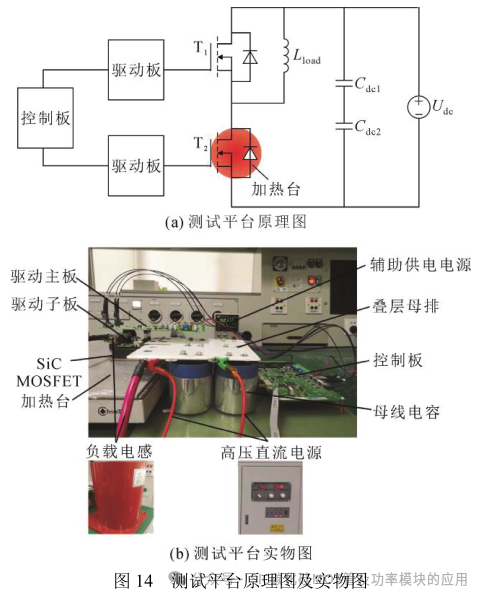

该文 基 于 3.3 kV/750 A 高压 大 功 率 SiC MOSFET 模块[1],搭建了如图 14 所示测试平台验证所提方法的可行性。

图 14(a)所示是测试平台原理图,由高压直流电源提供 Udc,Cdc1 和 Cdc2 串联组成母线电容,Lload为负载电感,T1 为辅助器件,T2 为被测器件,通过控制板给驱动板发送脉冲信号。正常开关测试时,Lload 取 50 μH 空心电感,控制板始终给 T1 驱动板发关断命令,给 T2 驱动板发双脉冲触发命令;HSF故障测试时,Lload 不接,控制板始终给 T1 驱动板发开通命令,给 T2 驱动板发短路单脉冲触发命令;FUL 故障测试时,Lload 取约 2 μH 空心电感,控制板始终给 T1 驱动板发关断命令,给 T2 驱动板发短路单脉冲触发命令。

图 14(b)所示为测试平台实物图,通过辅助供电电源给控制板和驱动板供电,控制板与驱动板通过光纤连接,母线电容经叠层母排与 SiC MOSFET 模块相连,SiC MOSFET 模块放置在温度可控的加热台上,驱动板分为主板和子板,子板直接安装在 SiC MOSFET 模块上,主板与子板通过排针连接。

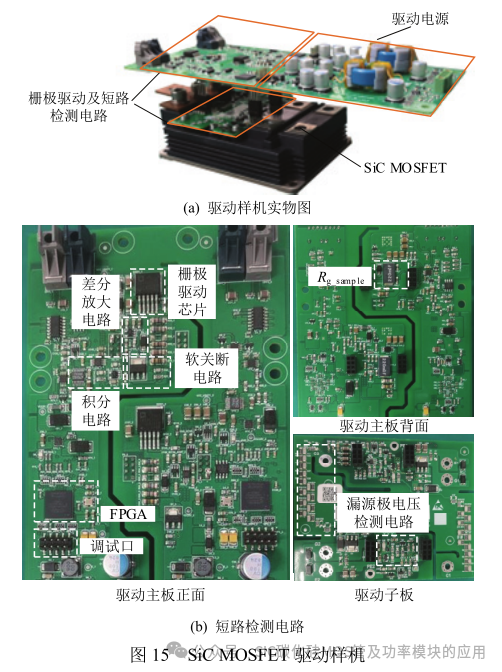

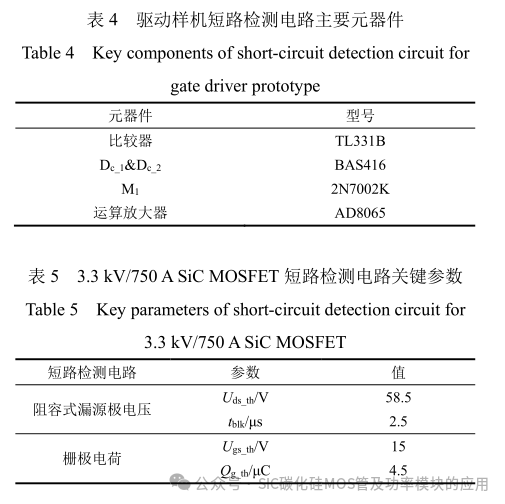

图 15 所示为采用该文所提短路检测方法的驱动样机。驱动样机主要由驱动电源、栅极驱动及短路检测电路 3 部分构成。逻辑控制单元采用英特尔现场可编程门阵列(field programmable gate array,FPGA)芯片 10M02SCU169I7G,驱动样机短路检测电路的主要元器件如表 4 所示。

根据式(2)、式(3)、表 1 和图 11、表 3 分析,3.3 kV/750 A SiC MOSFET 短路检测电路关键参数取值如表 5 所示。

在实际工程应用中,为避免 uds、ugs 高频振荡导致输出窄脉冲 Ssc_desat 和 Ssc_gate 引起保护误动,有必要滤除窄脉冲干扰。因此,通过 FPGA 设置tfilter=0.5 μs 的数字滤波时间,滤除脉宽不足 tfilter 的Ssc_desat 和 Ssc_gate 信号。

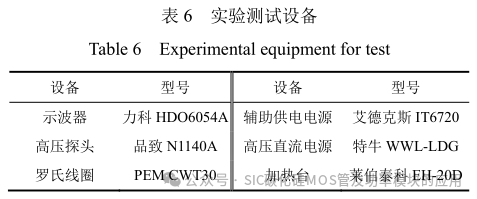

基于图 14 实验平台,测试该文驱动样机的短路保护效果,实验测试设备如表 6 所示。

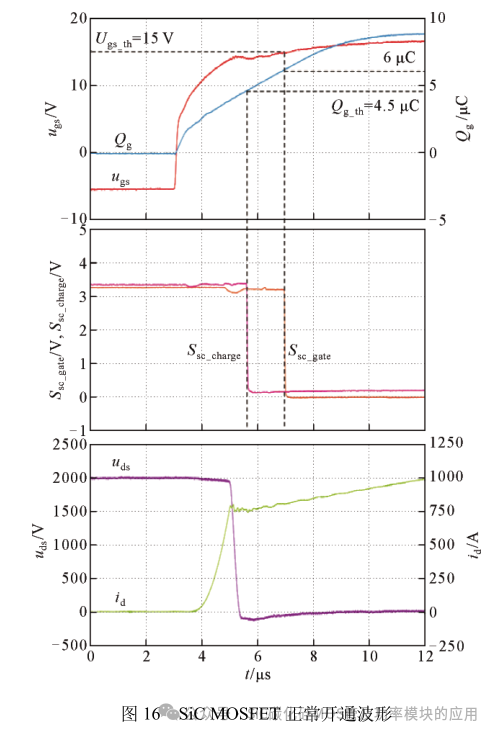

图 16 给出 Udc=2 kV,IL=750 A,Tc=25 ℃,SiC MOSFET 的正常开通波形。

从图 16 可知,当 Qg>Qg_th 时,Ssc_charge 翻转,当 ugs>Ugs_th 时,Ssc_gate 翻转;正常开通过程,ugs>Ugs_th时,Qg>Qg_th,不满足式(7)所示判断条件,栅极电荷短路检测未误动。

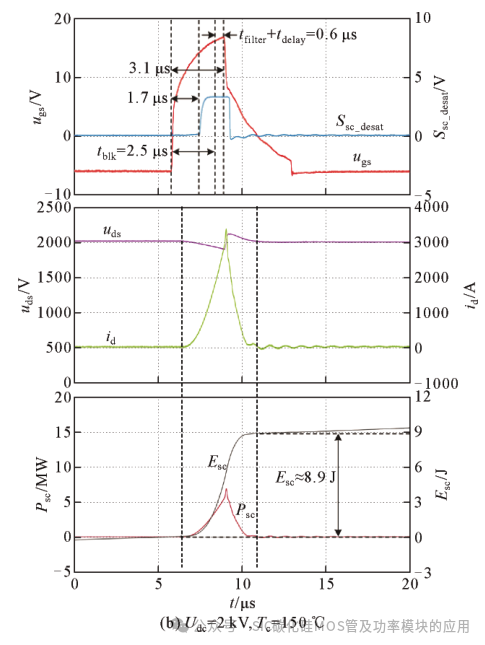

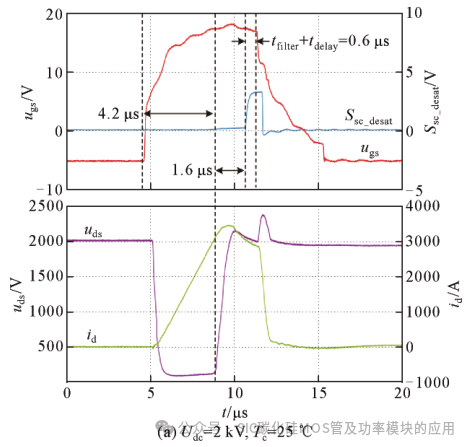

图 17 给出不同壳温和母线电压下,采用阻容式漏源极电压检测电路识别 HSF 故障的实验波形。

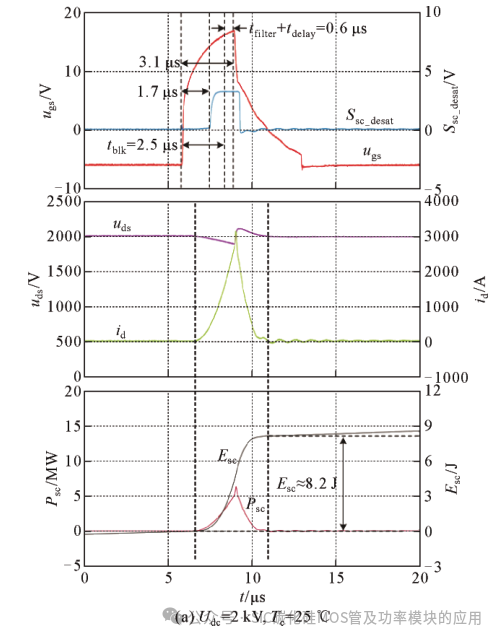

如图 17(a)所示,当 Udc=2 kV,Tc=25 ℃时,Ssc_desat 约在 1.7 μs 后翻转,此时在 tblk=2.5 μs 内,FPGA 屏蔽 Ssc_desat 信号,tblk 结束后,Ssc_desat 有效高电平脉宽仍大于 tfilter=0.5 μs 的滤波时间,FPGA 识别到 HSF 故障,并下发关断命令,经 tdelay=0.1 μs传输延时后 SiC MOSFET 软关断,同时 M1 导通,闭锁退饱和检测功能,Ssc_desat 翻转至低电平,此工况下 , 阻 容 式 漏 源 极 电 压 短 路 检 测 响 应 时 间 约3.1 μs,短路峰值电流 Isc_max 约 3.2 kA,短路峰值功率 Psc_max 约 6.4 MW,短路能量 Esc 约 8.2 J。

如图 17(b)所示,当 Udc=2 kV,Tc 从 25 ℃升高至 150 ℃,阻容式漏源极电压短路检测响应时间仍约 3.1 μs,Isc_max 约 3.4 kA,Psc_max 约 7.0 MW,Esc约 8.9 J;由实验结果可知,温度升高对阻容式漏源极电压短路检测响应时间影响不大,但短路峰值电流、短路峰值功率和短路能量随着温度升高而略有增加,这主要是 SiC MOSFET 的 Uth 呈负温度特性,gm 呈正温度特性导致。

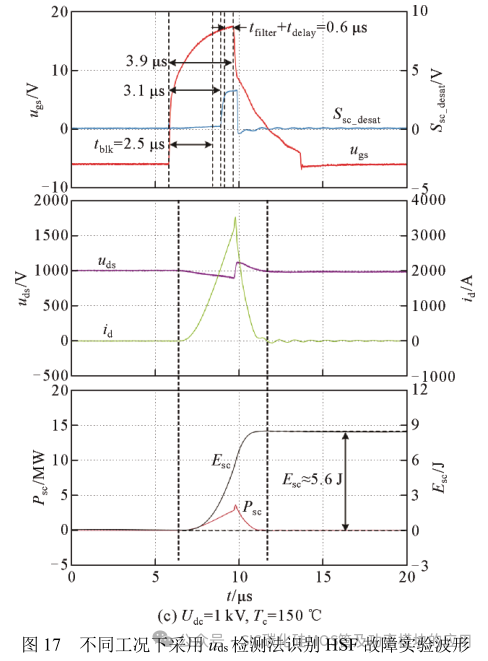

如图 17(c)所示,当 Tc=150 ℃,Udc 从 2 kV 下降至 1 kV,Ssc_desat 约在 3.1 μs 后翻转,阻容式漏源极电压短路检测响应时间增大至约 3.9 μs,Isc_max 约3.5 kA,Psc_max 约 3.6 MW,Esc 约 5.6 J;由实验结果可知,随着 Udc 降低,Cbl 的充电速率减慢,Ssc_desat在 tblk 结束后仍未翻转,导致阻容式漏源极电压短路检测响应时间明显增加。

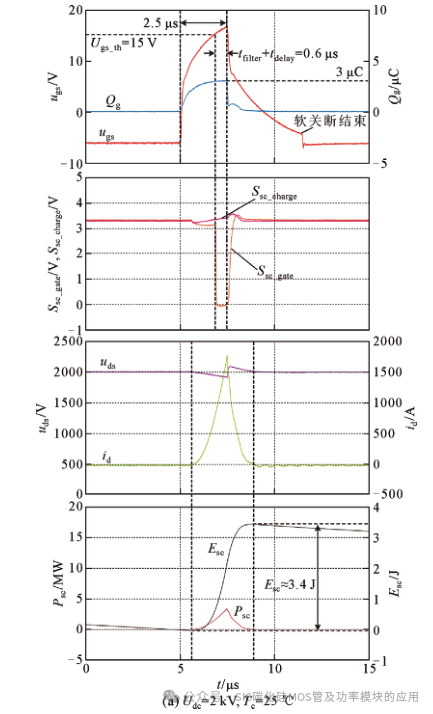

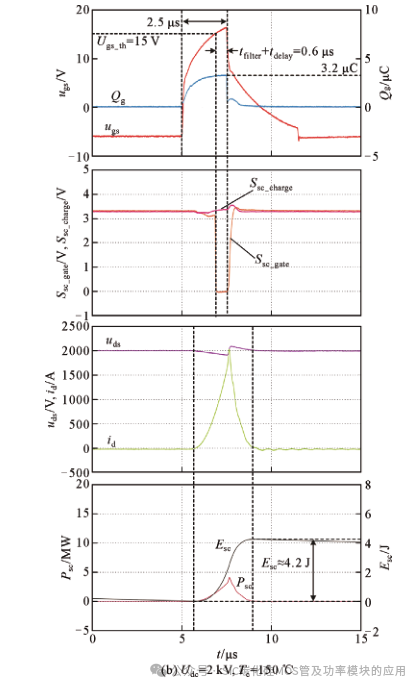

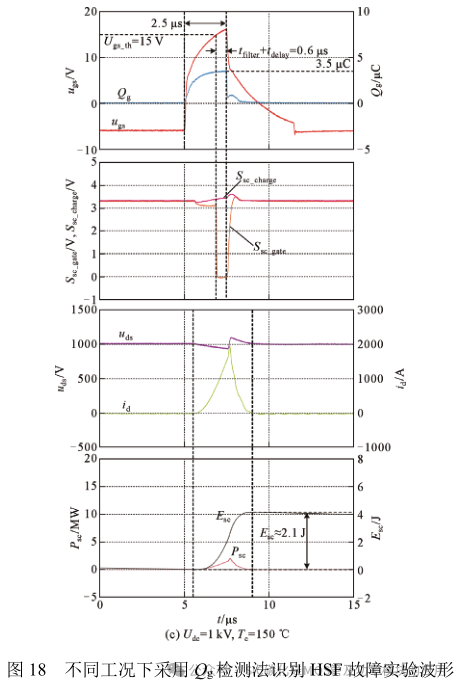

图 18 给出了不同壳温和母线电压下,采用该文所提方法的栅极电荷检测电路识别 HSF 故障的实验波形。

如图 18(a)所示,在 Udc=2 kV,Tc=25 ℃工况下,当 ugs>Ugs_th 时,Ssc_gate 翻转,有效低电平 Ssc_gate 经tfilter=0.5 μs 滤波后,Qg 仍约 3 μC,Qg<Qg_th,Ssc_charge未翻转,满足式(7)判断条件,FPGA 识别到 HSF 故障,并下发关断命令,经 tdelay=0.1 μs 传输延时后SiC MOSFET 软关断,同时闭锁栅极电荷积分功能,Qg 清零。栅 极 电 荷 短 路 检 测 响 应 时 间 约 2.5 μs,Isc_max 约 1.8 kA,Psc_max 约 3.4 MW,Esc 约 3.4 J。

如图 18(b)所示,当 Udc=2 kV,Tc 从 25 ℃升高至 150 ℃时,栅极电 荷短路检测 响应时间仍 约2.5 μs,Isc_max 约 2.1 kA,Psc_max 约 4.1 MW,Esc 约4.2 J;由实验结果可知,温度升高对栅极电荷短路检测响应时间影响不大,但短路峰值电流、短路峰值功率和短路能量也会随着温度升高而有所增加。

如图 18(c)所示,当 Tc=150 ℃,Udc 从 2 kV 下降至 1 kV 时,栅极电荷短路检测响应时间仍约2.5 μs,Isc_max 约 1.9 kA,Psc_max 约 2.0 MW,Esc 约2.1 J;由实验结果可知,栅极电荷短路检测响应时间不随 Udc 的降低而增加。

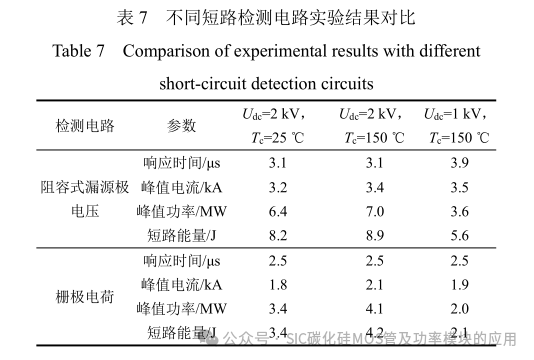

表 7 给出了分别采用常规阻容式漏源极电压检测电路和该文所提方法的栅极电荷检测电路识别HSF 故障的实验对比结果。

由实验结果可知,两种短路检测电路响应时间受温度影响不大,但短路峰值电流、峰值功率和短路能量随温度升高略有增加;当 Udc=2 kV,相比常规阻容式漏源极电压检测,该文所提方法的栅极电荷检测响应时间缩短了 0.6 μs,短路峰值电流和峰值功率明显减小,Tc=25 ℃时,短路能量降低约58.5 %,Tc=150 ℃时,短路能量降低约 52.8 %;此外,随着 Udc 降低,常规阻容式漏源极电压检测响应时间明显增加,而该文所提方法的栅极电荷检测响应时间仍保持不变,当 Udc=1 kV,Tc=150 ℃,相比常规阻容式漏源极电压检测,该文所提方法的栅和峰值功率显著减小,短路能量降低约 62.5 %。因此,该文所提方法采用栅极电荷检测电路识别高压大功率 SiC MOSFETs 的 HSF 故障优势明显,且随母线电压降低,优势进一步扩大。

图 19 给出了 Udc=2 kV,不同 Tc 下采用该文所提方法的阻容式漏源极电压检测电路识别 FUL 故障的实验波形。

从图 19 可知,Tc=25 ℃,FUL 故障下 uds 先下降到通态压降,约 4.2 μs 后 SiC MOSFET 才退出电流线性区,此时 tblk 已结束;从器件开始退出线性区到 Ssc_desat 翻转约 1.6 μs,比 HSF 故障减小约0.1 μs,这主要是快速变化的 duds/dt 通过 Cdesat 支路加快 Cbl 的充电速度导致,当 Ssc_desat 有效高电平脉宽大于 tfilter=0.5 μs 的滤波时间,FPGA 判断识别到FUL 故障,并下发关断命令,经 tdelay=0.1 μs 的传输延时后 SiC MOSFET 软关断,同时 M1 导通,闭锁漏源极电压检测功能,Ssc_desat 翻转至低电平。当 Tc从 25 ℃升高至 150 ℃,除 SiC MOSFET 短路峰值电流和 uds 关断尖峰略有增加外,阻容式漏源极电压检测响应时间基本不变。

3 结论

论文 基 于 3.3 kV/750 A 高压 大 功 率 SiC MOSFET 的器件特性,详细对比分析了几种常用短路检测方法的适用性,提出一种阻容式漏源极电压检测 与 栅 极 电 荷 检 测 相 结 合 的 高 压 大 功 率 SiC MOSFETs 短路保护方法,并设计驱动样机对所提方法的有效性进行验证。所得主要结论如下:

1)相比低压小功率器件,高压大功率 SiC MOSFETs 开通过程减慢,漏源极电压检测消隐时间增大,HSF 故障检测响应时间明显增加。

2)相比低压小功率器件,短路故障下高压大功率 SiC MOSFETs 漏极电流变化率显著降低,导致寄生电感检测电路输出电压幅值太小,抗干扰能力减弱,保护容易误动。

3)相比低压小功率器件,高压大功率 SiC MOSFETs 转移电容明显增加,正常开通和 HSF 故障下的栅极充电电荷差异更大,大幅提高了栅极电荷检测电路工作可靠性。

4)所提短路保护方法识别 HSF 故障优势明显,保护 响 应 时 间 缩 短 了 1.4 μs ,短 路 能 量 降 低 了62.5 %;且能可靠识别 FUL 故障。