文章来源:罗姆(ROHM)半导体

摘要:SiC MOSFET 可作为开关器件用于各种开关电源中,因为其导通状态可通过在栅极和源极之间施加一定电压来控制。除了降低传导损耗外,开关器件还必须降低开关损耗并将 EMC 噪声降至最低,而这可以通过设计在栅极和源极之间施加电压的方法来实现。为了考虑如何充分发挥 SiC MOSFET 的潜力,首先有必要了解在栅极和源极之间施加电压时发生的基本动作(状态转换)。本文总结了 SiC MOSFET 在栅极和源极之间施加电压时发生的状态转换,旨在为设计能充分发挥其性能的栅极驱动电路提供指导。

1. 关于 SiC MOSFET

1.1 SiC MOSFET 的重要性

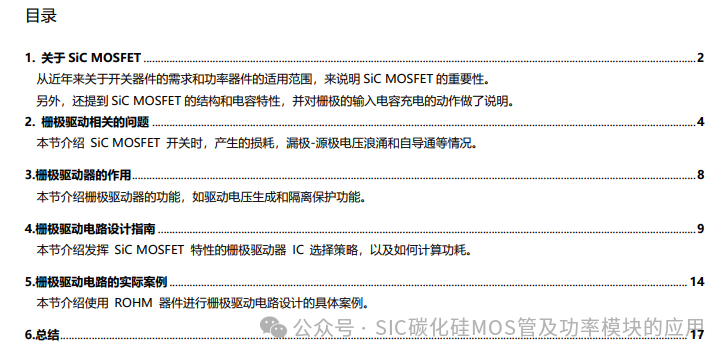

近年来,车辆和我们周围各种物体的电气化进程日新月异,如何更有效地控制电能已成为一项技术挑战。功率控制一般涉及改变功率的形式,例如通过接通和断开电流调整从电源向负载提供的功率大小,或将直流电转换为交流电。图 1 显示了开关频率和负载电容的适用范围。

近年来,节能和设备小型化的需求日益增长。通过将开关频率提高到更高的频率,可以使电感器和电容器等无源元件的体积更小。频率越高,开关损耗越大。具有良好开关特性的SiC MOSFET 具有最广泛的应用范围,在实现高频和节能方面正变得越来越重要和负载能力的适用范围。

1.2 SiC MOSFET 的基本构造

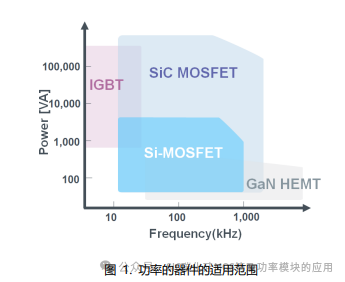

SiC MOSFET 的结构如图 2 所示。通过在漏极和源极之间施加漏极极性为正的电压(VDS)以及在栅极和源极之间施加栅极极性为正的电压(VGS),电子被吸引到 P 型半导体区域,并形成一个 n 型沟道(反转层)。电流通过该沟道从漏极流向源极。这种机制使 MOSFET 能够通过电压实现开关控制,通过 n 型沟道实现高速,并通过垂直结构实现高耐压。

根据栅极结构和漂移层结构的不同,SiC MOSFET 大致可分为平面结构(图 2-(a))和沟槽结构(图 2-(b))。

・平面型构造如图 2-(a) 所示,栅极是在晶圆表面形成的。因此,由于通道横向形成,单个单元尺寸就会变大。

・沟槽型构造如图 2-(b)所示,沟槽结构是从晶圆表面向漏极方向挖沟槽,并嵌入栅极电极。在这种结构中,沟槽是垂直形成的,从而实现了单元的微型化。因此,可以比平面结构排列更多的单元格,降低导通电阻。

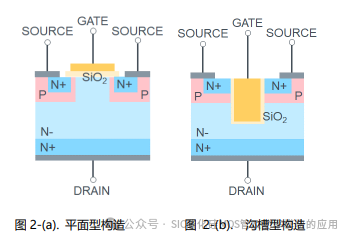

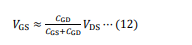

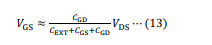

1.3 寄生容量特性

SiC MOSFET 有源极电极、栅极电极和漏极电极,这些电极的组合会产生寄生电容。源极和栅极之间的电容为 CGS,漏极和栅极之间的电容为 CGD,源极和漏极之间的电容为 CDS。CGD由作为电介质的栅极氧化膜形成的电容决定,CGS 由在栅极-源极之间形成的电容 CO和 P 通道以及 N 通道和以氧化膜为电介质形成的 CP、CN+的总和决定(CGS=CO+CP+CN+)。另外,CDS是漏极-源极之间的接合电容。(图 3)

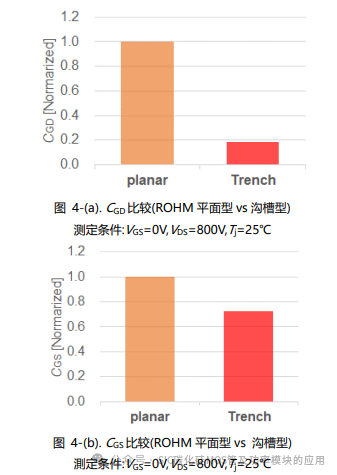

单一单元构造中栅极氧化膜纵向深的沟道结构,往往具有较高的寄生电容。但是,ROHM 的 SiC MOSFET 通过工艺技术的进步,利用沟道结构可以降低导通电阻的特征,减小芯片尺寸来降低芯片整体的寄生电容。图 4 是 ROHM 第二代平面结构 SiC MOSFET 和第四代沟槽结构 SiC MOSFET 的栅极电容比较。尽管第 4 代是沟槽结构,通过单元的微细化,实现了比平面结构更小的寄生电容。

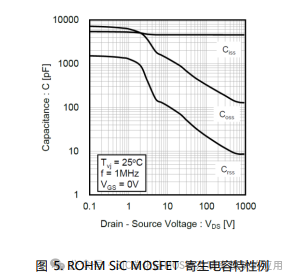

这里的寄生电容通常在 MOSFET Datasheet 中(Ⅰ)/输入电容(Ciss)、(Ⅱ)/输出电容(Coss)和(Ⅲ)/反馈电容(Crss)三个参数表示。这些都是影响开关特性的重要参数。

(Ⅰ). 输入电容: Ciss = CGD+CGS

要打开/关闭 MOSFET,必须对 Ciss 充电/放电,这会影响延迟时间;对 Ciss 充电所需的电量为 Qg

(Ⅱ). 输出电容 : Coss = CDS + CGD

Coss 会影响关断特性:如果 Coss 较高,因为关断时需要更多时间对 Coss 充电,关断时间会更长

(Ⅲ). 反馈电容 : Crss = CGD

Crss 会影响开关速度。当 Crss 较大的时候,漏极-源极电压的导通和关断时间较长。

另外、Ciss, Coss, Crss 还与漏极-源极电压 VDS 有关。如图 5 所示,随着 VDS 的增大、电容值趋向减小。

1.4 栅极充电特性

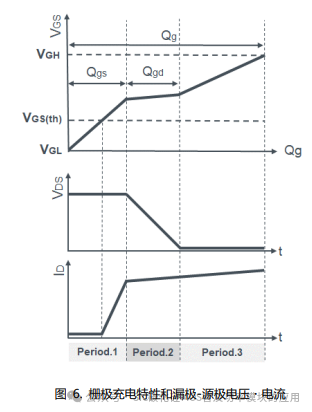

图 6 是栅极充电特性的示例, SiC MOSFET 的栅极充电特性是决定驱动电流和驱动损耗的参数。大致可以分为三个阶段。

Period.1

栅极电压上升,到达米勒电压的期间。向栅极源极间电容 CGS充电使栅极电压上升。超过 VGS(th)之后,漏极-源极之间的电流开始流动。另外,漏极电流增加后,漏极源极电压(VDS)下降。

Period.2

VDS 变化,栅极-漏极电容 CGD 放电。这个期间被称为米勒期间,栅极-源极电压不会上升。另外,这个时候的栅极电压被称为平台电压。

Period.3

当 CGD 的电压与 CGS 的电压相同时,开关操作完成,漏极-源极间电压不再变化,然后再次开始对 CGS 和 CGD 充电,栅极电压开始上升。

为了加快漏极-源极电压的变化,选择 CGD 小的器件,或者为了缩短米勒时间,加大对 CGD 放电的电流。

2. 栅极驱动相关的问题

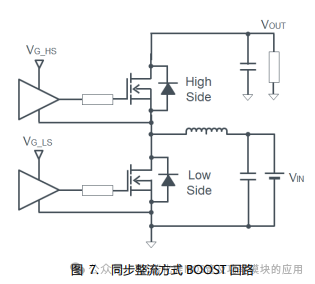

本节将举例说明在设计栅极驱动电路时,使用同步整流BOOST 电路(图 7),SiC MOSFET 在开关时可能出现的问题。

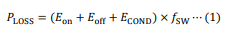

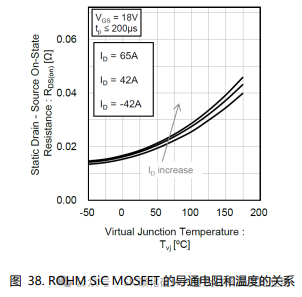

2.1 器件的发热/功率损耗大

驱动电感负载的器件中产生的功率损耗(PLOSS),如图 8 所示,在开关的导通/关断时,由于电压和电流的重叠而产生的开关损耗(Eon/Eoff),以及由导通时流过的电流和器件的导通电阻决定的导通损耗(ECOND)。由于每次开关发生,开关频率(fSW)的乘积为器件的功耗 PLOSS,如公式(1)所示。

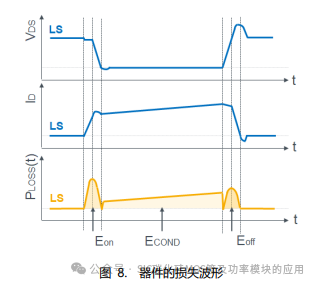

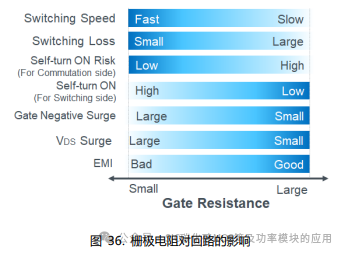

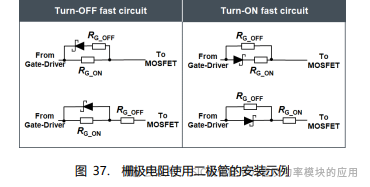

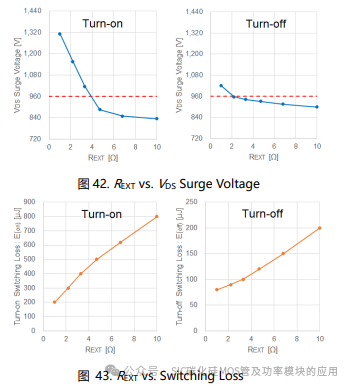

降低功率损耗的方法之一是降低开关频率,但如果选择较高开关频率的优势,则需要使用栅极驱动电路来抵消这一问题。图 9 是栅极电阻的大小与导通损耗(Eon)和关断损耗(Eoff)之间的关系。图 10 是栅极电阻 (RG_EXT) 与开关速度 (dV/dt)之间的关系。如图 10 所示,栅极电阻 (RG_EXT) 越小,开关速度 (dV/dt) 越高,VDS 变化时间就越短,这是由于栅极电阻(RG_EXT) 越小,开关速度 (dV/dt) 越高,VDS 变化时间就越短。

2.2 漏极-源极电压(VDS)的浪涌电压大

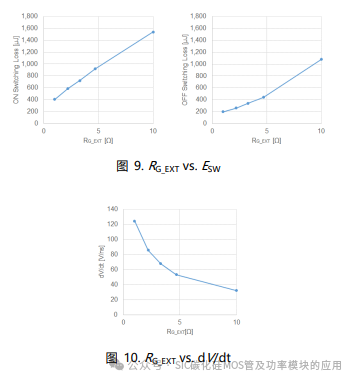

Low Side 的 MOSFET 在关断时,漏极-源极电压 VDS 上升到输出电压(VOUT),但由于电流路径的电感成分,产生浪涌电压。

作为降低 VDS 浪涌电压的方法,也有在漏极-源极之间设置snubber 电路的方法,不过,作为栅极驱动电路能做的对策,也通过增大外接栅极电阻值 RG_EXT 来降低开关速度的方法。图11 表示栅极电阻(RG_EXT)和漏极-源极电压浪涌的变化。

2.3 栅极-源极电压(VGS)的”正电压上升 “或 “负浪涌电压”

虽然重点往往放在 VDS 和 ID 的变化上,但也必须考虑这些变化对栅源电压 (VGS-HS) 的影响。在应用说明 「桥式结构中的栅极-源极电压的动作」 *1 中对此进行了详细说明,本应用说明也将再次说明一下。

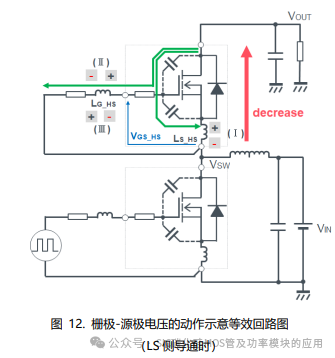

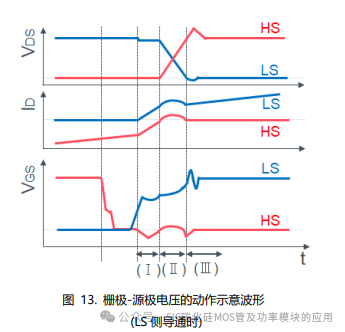

低压侧 (LS) 在导通时的行为如等效电路图(图 12)和波形(图 13)所示:在 LS 导通时,ID 首先发生变化;LS 的 ID 趋于增大,而高压侧 (HS) 的 ID 趋于减小,因此事件(Ⅰ),使得图 12 (Ⅰ)中表现出极性起电发生。由于这个起电的电流对CGS-HS 充电,源极为正,因此在 HS 中 VGS-HS 被拉到负侧,表现为 “负浪涌”;当 ID 变化结束时,LS 侧 VDS 的电位降低;

如图 13(II)所示,HS 和 LS 在 VGS-HS 处分别出现 “正电压上升”。因此,本应关闭的 HS 侧会根据 VGS-HS 的上升程度启动导通动作(自开启)、与 LS 侧的导通动作重叠,导致上下 MOSFET 同时接通,从而产生直通电流。CGS 的充电电流持续流动,直至接通操作完成,储存在 LG_HS,不过,在 VSW 的变化结束的时消失,LG_HS 像如 12(Ⅲ)一样起电。因为这个起电,再次再次表现为 “负浪涌”。

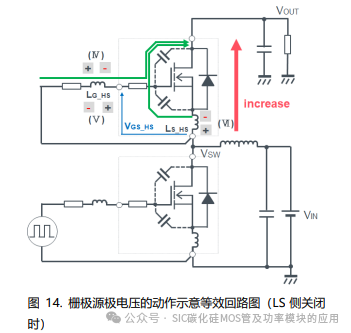

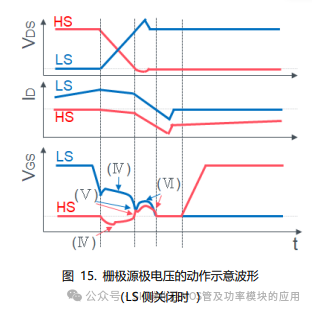

接下来,对 LS 侧关闭时的动作进行说明。LS 侧的关闭时的动作等效电路图(图 14)和波形(图 15)所示。

与接通时一样,每个事件都编号为 (IV)、(V) 和 (VI)。与导通相比,基本动作相同,只是 VDS 和 ID 的变化顺序有所改变,对应如下

关闭 导通

事象(Ⅳ) → 事象(Ⅱ)

事象(Ⅴ) → 事象(Ⅲ)

事象(Ⅵ) → 事象(Ⅰ)

HS 侧的 VGS “负浪涌 “为事件 (Ⅳ)。

事件 (Ⅵ)导致的 VGS 升高已在关断结束之前,因此,即使 HS 侧处于导通运行状态,LS 侧仍处于关断状态,而且几乎不成问题。

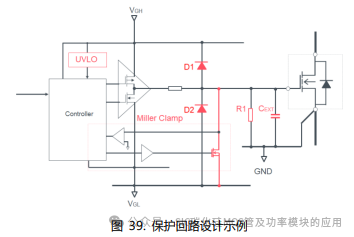

2.4 正电压上升导致自导通(误点弧)的发生

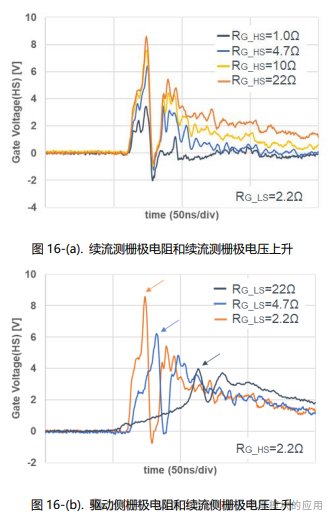

在导通过程中(事件 II),当栅极电压超过栅极阈值电压VGS(th) 时,由于正侧电压上升,会发生自导通,从而导致意外接通。正电压上升与 LS 侧的开关速度和栅极电阻 (RG_HS)有关,如果 LS 侧的开关速度较慢,而 HS 侧的栅极电阻(RG_HS) 较小,则自导通发生的可能性较小。图 16 是驱动侧(LS) 接通时,续流侧 (HS) 的栅极-源极电压波形。栅极电阻(RG_HS) 越大,栅极电压上升越大(图 16-(a)),而驱动侧 (LS)的栅极电阻 (RG_LS) 越小,开关速度越快,栅极电压上升越大(图 16-(b))

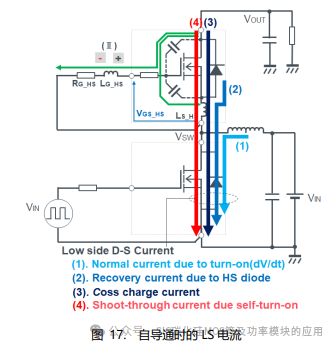

发生自导通时,如图 17 所示,LS 侧的漏极-源极电流观测到以下 4 个电流。

➀正常开启电流

②HS 侧二极管的恢复电流

③自导通电流

④Coss 充电电流

因此,很难确定是否发生了自导通。此外,由于所评估的波形包含了器件内阻的影响,因此简单地判断栅极波形是否超过 VGS(th) 也不是一个好的标准。

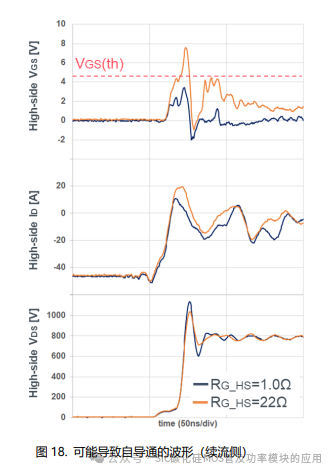

图 18 是将续流侧的栅极电阻(RG_HS)设为 1Ω 和 22Ω 时的波形比较。RG_HS 为 22Ω 时,发生大的栅极电压上升,超过 VGS(th)约 10ns。此时,由于自导通电流增加,续流侧的 VDS的斜率变小,峰值降低。另外,驱动侧的漏极-源极电流增加。

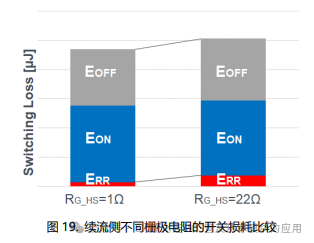

如图 19 所示,从开关损耗方面进行比较,RG_HS=22Ω 时,开通恢复损耗 ERR(※包括看似自开通的电流波形)略高,但导通损耗(Eon)和关断损耗(Eoff)几乎没有变化、 可以说,自导通的影响很小。

可以通过判断高温下的开关损耗(此时 VGS(th) 较低)或比较负偏压下的损耗和 0 V 下的关断损耗(两者无明显差异)来确认。

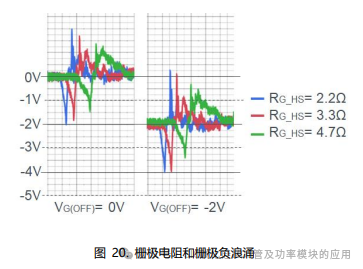

2.5 负浪涌电压的发生

由于栅极电阻和栅极负电压的设置,驱动侧关断时续流侧的栅极波形如图 20 所示。可以看出,栅极负电压不会产生栅极负浪涌效应。栅极电阻越大,负浪涌效应往往越小。

3. 栅极驱动器的作用

在设计栅极驱动电路时,首先需要了解栅极驱动器的作用,因此其主要作用如下。

3.1 功率器件的输出

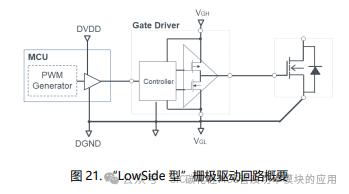

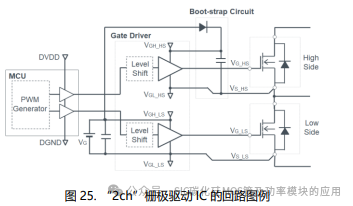

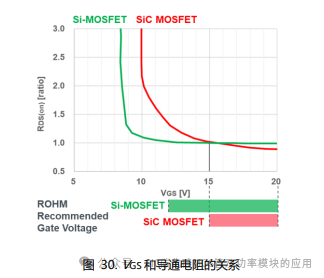

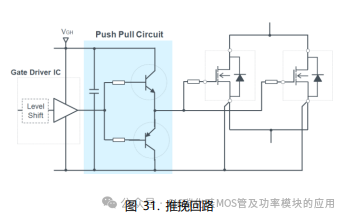

驱动电压功率器件的推荐驱动电压取决于器件和制造商;对于ROHM 的 SiC MOSFET,建议栅极源极正电压为 15~18 V(VGH),栅极源极负电压为 0 V (VGL)。作为栅极信号主要来源的控制器 (MCU) 是 5 V/3.3 V (DVDD) CMOS 输出,栅极驱动器的作用之一是以 15 V 以上的电压驱动功率器件,以最佳方式驱动功率器件。图 21 显示了为输出功率器件驱动电压而设计的 LowSide 栅极驱动器的电路图。

3.2 驱动快速开关的功率器件

作为栅极信号源的控制器(MCU)的电流能力一般小于 0.1A,无法直接驱动功率器件;以 MOSFET 的输入电容为 5nF、控制器 I/O 端口的输出阻抗为 500Ω 为例,时间常数 t 的值如下𝑡 = 𝐶𝑅 = 5𝑛 × 500 = 2.5 [µ𝑠]栅极的导通/关断速度变得非常慢,导致开关损耗很高。为了优化功率器件的驱动,栅极驱动器的作用之一就是高速驱动功率器件。

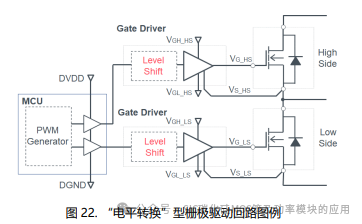

3.3 控制电路的电平转换

图 22 是一个具有电平转换功能的栅极驱动电路示例。在大多数情况下,作为栅极信号源的微控制器 (MCU) 的 GND电平与功率器件的源电平(VS_HS,VS_LS)往往是不同的,为了施加最佳的栅极-源极电压,需要对 MCU 信号进行电平转换,这是栅极驱动器的重要作用之一。

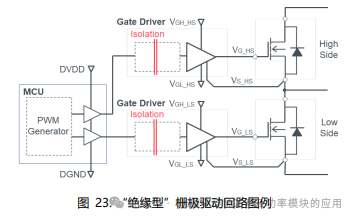

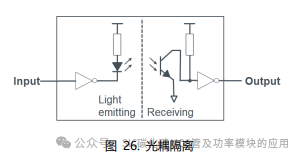

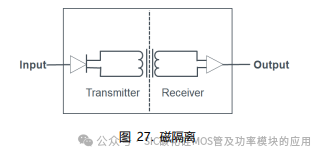

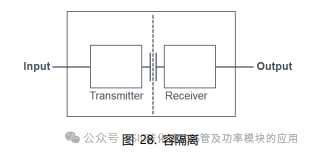

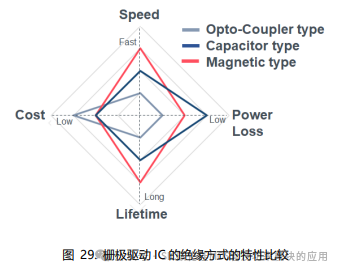

3.4 隔离控制电路和电源电路

在使用功率器件的应用中,主电路的总线电压可处理几百伏或更高的电压,功率器件漏极-源极之间的电流可达几十安或更高。如果控制系统和电源系统之间没有绝缘,万一发生漏电,产品本身没有足够的绝缘措施的话,或者由于系统故障导致电子元件损坏,用户可能会触电。使用具有隔离功能的栅极驱动器集成电路可降低用户触电的风险。图 23 是绝缘型栅极驱动回路的示例。因此,使用具有绝缘能力的栅极驱动 IC,可以减少客户触电的风险。

4. 栅极驱动电路设计指南

栅极驱动电路由栅极驱动及其外围电路组成;栅极驱动器一般采用集成电路。

为了器件的最优化,如图 24 所示,需要选择栅极 IC、选择栅极电阻、设计栅极驱动电压和电流驱动能力以及设计保护电路。栅极驱动器电路的基本设计项目如下。

4.4 栅极驱动电路的功耗

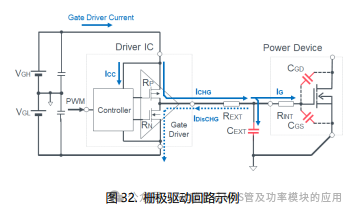

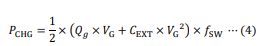

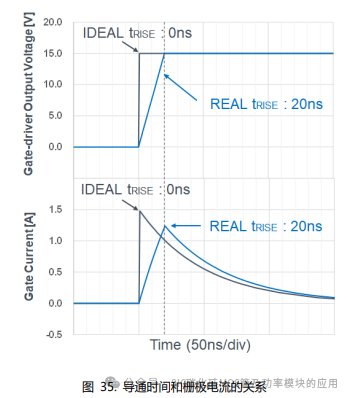

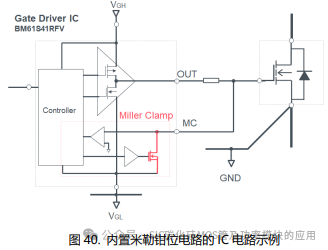

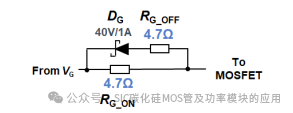

本节介绍栅极驱动电路消耗的功率。图 32 是一个使用栅极驱动器 IC 的栅极驱动回路示例。

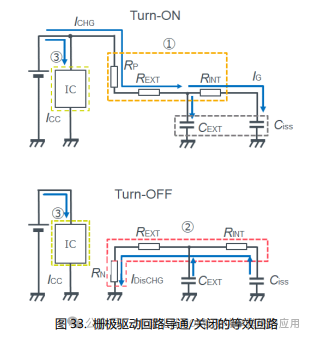

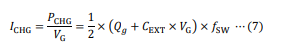

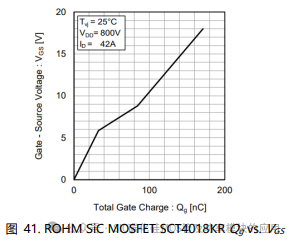

要打开栅极,必须对输入电容 Ciss(CGS+CGD)或栅-源极之间的电容(CEXT)充电。 另外、要关断的话,必须对已充电的电荷进行放电。图 33 是 图 32 的导通/关断等效电路的充电电流(ICHG)、放电电流 (IDisCHG) 和栅极驱动器 IC 消耗的电流 (ICC)。

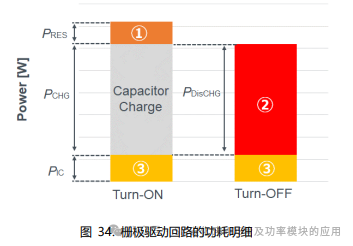

栅极驱动电路的功耗 PGDR 包括:开启的时候,对电容元件充电时在 RP、REXT、RINT 处产生的损耗 PRES (➀);关断期间对电容元件放电时在 RINT、REXT、RN 处产生的功耗 PDisCHG(②);栅极驱动器集成电路消耗的功率总和 PIC(③),可用公式 (2)表示。

𝑃GDR = 𝑃RES + 𝑃DisCHG + 𝑃IC ⋯ (2)

图 34 是耗电量的明细。可以看出 PCHG 发生的损耗和储存在电容中能量相等。

图 44. 选定的栅极电阻

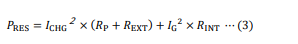

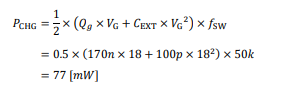

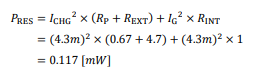

导通时电容元件充电的时候,电阻产生的功耗 PRES 由公式(3)得出以下值:

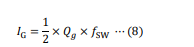

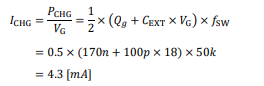

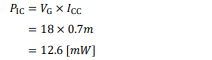

栅极驱动 IC 的功耗由公式(8)得出:

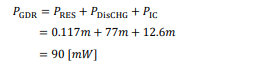

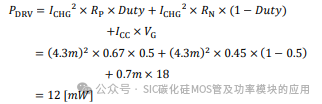

栅极驱动电路的功耗 PGDR 由公式(2)得出以下结果:

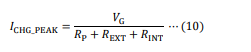

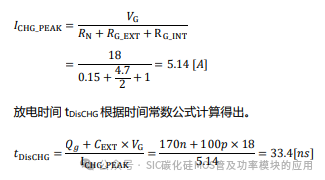

栅极驱动电路的峰值电流 ICHG_PEAK 由公式(10)计算得出。根据栅极驱动 IC 的 datasheet,栅极驱动 IC 充电侧晶体管的输出电阻 RN 的最小值为 0.3Ω,放电侧晶体管的输出电阻RN 的最小值为 0.15Ω,因此可以计算出放电时的最大峰值电流。

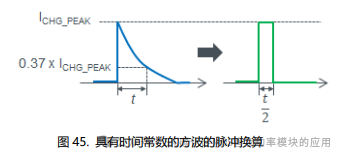

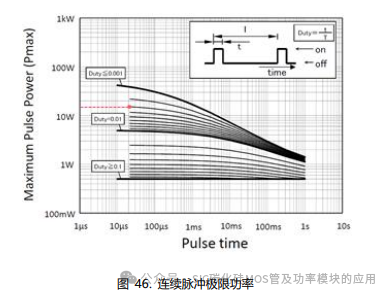

如图 45 所示,将具有 f 时间常数的方波进行脉冲换算,则以峰值电流为 5.14A、脉冲持续时间 (t/2) 为 16.2ns 计算。

𝐷𝑢𝑡𝑦 = 𝑡 × 𝑓𝑆𝑊 × 2 = 33.4𝑛 × 50𝑘 × 2 = 0.0033

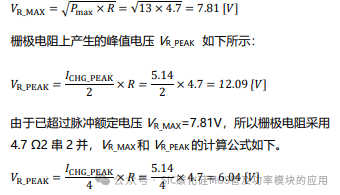

从图 46 中可以读出电阻的连续脉冲极限功率约为 13W。

电阻的额定脉冲电压由以下的公式计算得出:

脉冲额定电压可以降低到 VR_MAX= 7.81 V 以下值。

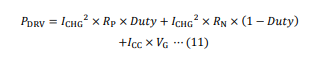

栅极驱动电路的功耗为 90 mW,这意味着栅极驱动电路的电源必须设计为 90 mW 以上的额定功率,并且不受最大 5.14A/33 ns 宽度的陡峭负载波动的影响。假设占空比为 50%,栅极驱动 IC 的功耗 PDRV,由公式 (11)得出:

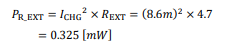

封装功率 Pd 为热阻为 180 °C/W,Pd = 694 mW,这证明栅极 IC 产生的热量不成问题。栅极电阻(REXT)的功耗 PR_EXT :

ROHM 耐浪涌电阻:如果选择 ESR10 的话,额定功率为250mW,平均功率不成问题。但因为脉冲功率会产生的瞬时热量会被积累,所以请进行热测量评估。

图 44 中的关断二极管(DG)选用 的是 40 V/1A 的产品。

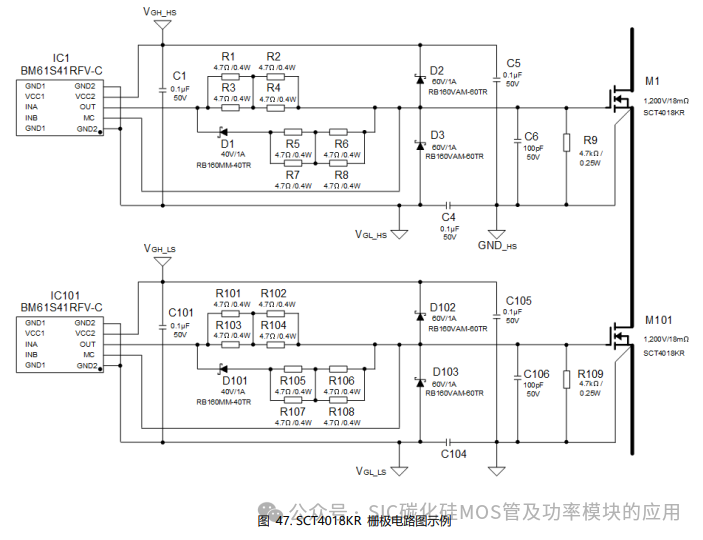

图 47 的设计示例中检讨的是采用 ROHM SiC MOSFETSCT4018KR 实现的栅极驱动电路图示例

6.总结

随着 SiC MOSFET 的替代,开关速度的提高,出现漏-源极电压浪涌和自导通等问题的风险也在增加。经过深思熟虑的栅极驱动电路设计将有助于避免问题的发生,并最大限度地发挥SiC MOSFET 的能力。

希望本应用说明中介绍的栅极驱动电路设计指南和保护电路设计示例能对栅极驱动电路设计有所帮助。