摘要:碳化硅(silicon carbide,SiC)金属–氧化物–半导体场效应管 (metal-oxide-semiconductor field effect transistor ,MOSFET)性能优越、发展迅猛,在工业界获得广泛应用。 其失效与结温息息相关,故SiC MOSFET 结温监控技术至关重要,近年来成为研究热点。文中将该技术分为经典结温监测、考虑老化影响的结温监测、结温控制3 部分。对于经典结温监测技术,重点介绍热模型法和热敏电参数法的原理、模型、发展历程、缺点及优势;对于考虑老化影响的结温监测技术,重点分析老化对结温监测的影响,论述老化补偿技术的必要性并指出现有方法的局限性;对于结温控制技术,分析其意义,重点介绍内部控制法和外部控制法的原理, 比较各类方法的优劣。最后,综合以上分析,指出SiC MOSFET 结温监控领域存在的关键问题和发展方向,旨在为相关研究人员提供参考。

关键词:碳化硅金属–氧化物–半导体场效应管;温变机理; 结温监测;结温控制;器件老化

0 引言

与硅(Si)基器件相比,碳化硅(SiC)金属–氧化物半导体场效应管(metal oxide semiconductor field effect transistor,MOSFET)性能优越,具有高击穿 电压、高功率密度、短开关暂态、低通态电阻、高导热率和高抗辐射能力等显著优势,因而在工业界获得广泛应用。著名市场调研公司Yole的报告显示,目前SiC MOSFET市场规模年增长率接近50%,5 年内市占率将达30%,最终与Si 基绝缘栅双极型晶体管(insulated gate bipolar transistor,IGBT)并驾齐驱。IGBT 多用于大功率变换器,而SiC MOSFET在中小功率、高频变换器中应用前景广阔。

SiC MOSFET 是变换器的核心,其运行状态关乎变换器系统的可靠性与工作性能,一旦故障, 极易造成巨大经济损失,危害公共安全。与Si 基器件相比,SiC MOSFET的独有特性带来了新的可靠性挑战。1)高功率密度意味着高单位产热,高开关频率则代表着高开关损耗,因此,SiC MOSFET工作温度一般高于 Si 基器件,另一方面,高电流密度易导致电迁移现象,从而在金属层中产生空缺;2)SiC MOSFET芯片体积缩小限制了其散热能力与短路耐受能力;3)SiC 杨氏模量高于Si, 在相同热应力下机械应力更大,易发生封装老化;4)SiC MOSFET门极氧化层比Si基器件更薄,易发生氧化层老化或电介质击穿。因此,提高SiC MOSFET 运行可靠性迫在眉睫。

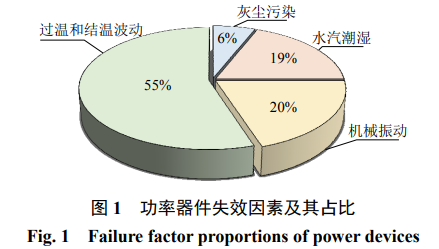

图1 为功率器件常见失效诱因及其占比。显然,结温过高与周期性波动是主导因素,占比超过50%。结温过高可导致器件瞬时失效,如热击穿、 隧道击穿、键合线熔化、焊锡层熔化等。结温周期性波动可引起器件封装老化并加速其发展,最终导致老化失效,如键合线脱落、铝金属层重构、焊锡层退化等。结温过高与结温波动可在电场复合作用下产生电–热应力,引起芯片本体的老化,如门极氧化层退化和MOSFET体二极管双极性退化。 此外,由Coffin-Manson-Arrhenius(CMA)模型可知, 功率器件的预期寿命和平均结温、结温波动幅值均呈负相关。因此,SiC MOSFET结温监测与控制技术至关重要。

首个应用于Si 基IGBT 的结温监控技术诞生于20世纪末。如今,此类技术历经30 年发展,日趋成熟。然而,SiC MOSFET 投入工业应用仅十余年,其特性与Si 基IGBT 迥然不同,故传统结温监控技术难以适用。SiC MOSFET 结温监控技术处于发展初期,相关理论体系缺失仍不健全。

因此,本文整理并分析SiC MOSFET 结温监控技术研究现状,介绍其发展历程,总结目前存在的关键问题,展望该领域的未来发展方向,以期能为相关研究人员提供参考。首先,结温监控技术可分为监测和控制两部分,前者是后者的基础,后者是前者的目标。根据是否考虑老化的影响,结温监测技术可进一步分为经典的和考虑老化影响(considering the aging effect,CAE)的结温监测技术。 现有多数结温监测方法属于前者。它们忽略器件老化影响,并假设器件参数在监测时段恒定,因而仅能在短期保证监测精度。CAE 结温监测技术能通过补偿老化影响,保证器件长期运行中的高监测精度。结温控制技术出现相对较晚,根据调控量可分为内部控制法与外部控制法。本文将按照SiC MOSFET 经典结温监测技术-CAE 结温监测技术–结温控制技术的顺序依次介绍各类方法的原理模型,分析其优劣,以促进我国宽禁带器件的蓬勃发展。

1 SiC MOSFET 经典结温监测技术

结温监测技术有两个基本要求:1)实时性, 可及时获取目标器件的结温信息,以用于状态评估与结温控制;2)在线性,测量结温不影响目标器件与变换器的正常运行,或产生的不良影响可接受。显然,离线结温测量不满足上述要求,故在此不予讨论。结温监测技术的难点在于测温设备无法接触被封装的器件芯片,导致测温结果不准。为此, 诞生了热模型法与热敏电参数(thermal sensitive electrical parameter,TSEP)法两大类经典结温监测方法。

1.1 基于热模型的结温监测方法

1.1.1 热模型法的基本原理

热模型法利用测温设备得到选定观测点的温度,然后根据观测点与目标器件芯片间的热网络与实时测量的损耗计算结温。观测点通常选为器件外壳或周围空气等易测温的位置。热电偶、热敏 电阻与红外热成像仪是测量观测点温度的常用手段。它们有时被划分为物理接触法和光学测量法,但本质上均属于热模型法。

1.1.2 一阶热模型法

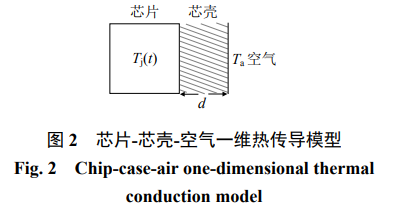

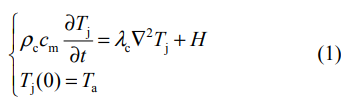

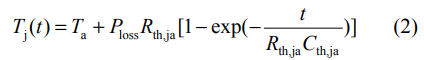

基于经典物理传热学可推导一阶热模型。仅考虑功率器件芯片法向温度分布时,可将其简化为一维热传导模型,如图2 所示。假设目标器件芯片温度时变且均匀分布,记作Tj;芯片密度为ρc,比热容为cm,单位体积产热功率为H;芯片壳厚度为d, 导热率为λc;环境空气温度恒为Ta。则该芯片的温度场方程为

式中Tj(0)为0 时刻的目标器件温度,通常等于Ta。 解式(1)可得:

式中:Rth,ja 为芯片–环境热阻;Cth,ja 为芯片–环境热容;Ploss 为芯片总损耗。当芯片处于热稳态,式(2)可简化为

以上为最简的功率器件一阶热模型,根据 Ta、Ploss和 Rth,ja即可计算出结温。

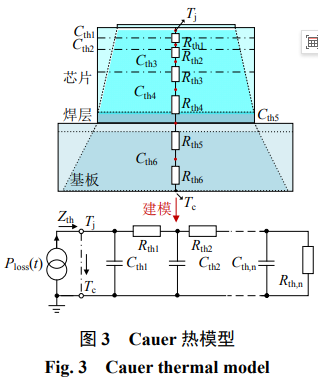

1.1.3 Cauer 热模型

功率器件一阶热模型的成立基于许多严苛假设,如芯片温度分布均匀、无二极管等其他热源、 芯壳导热率均匀、忽略辐射对流等。这些假设与实际情况相差甚远,导致热模型计算误差大。为提高结温求解精度,多阶热模型被广泛采用。Cauer 热模型是最典型的多阶热模型,如图3 所示。首先, 将功率器件沿法向分层,每层热阻和热容用Rthi 和Cthi 表示(i=1,2,⋅⋅⋅);然后,建立热阻–热容等效电路模型(损耗对应电流、温度对应电位、热容对应电容、 热阻对应电阻);最后,基于电路原理求解结温。Cauer热模型的缺陷在于所有分层热容共享同一温度参考点,因此,当参考点温度变化时,分层热容需重新估算。

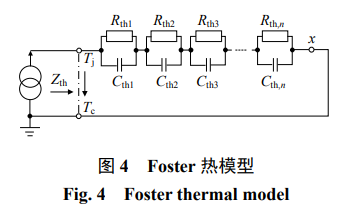

1.1.4 Foster 热模型

为解决Cauer 热模型存在的问题,研究者提出了Foster 热模型,如图4所示。Foster 热模型每层热阻抗具有相同的阶数与频率响应特性,故参考点温度变化不影响前级热阻–热容参数,其模型简单。然而,Foster 热模型各节点无法与实际物理模型对应,其关键参数只能通过结温和传感器测量点间温差推算,建立过程繁琐。

1.1.5 热模型法的发展

热模型法不仅可用于SiC MOSFET,还可用于IGBT 乃至所有功率器件。热模型法的关键难题在于如何平衡模型精度与计算复杂度。

近年来,有研究者在传统热模型的基础上提出了三维耦合热模型。该模型不仅考虑了热传导效应,还考虑了功率器件与空气间的热辐射效应, 提高了结温监测的极限精度,但极大增加了计算复杂度。

传统热模型结温求解算法基于拉普拉斯(Laplace)变换,即在式(3)基础上将高阶热阻抗表示为一系列与时间以及热时间常数有关的一阶热阻抗之和,并在时域内求解。然而,随着芯片分块数n增加,理论上需要考虑的热阻数量为组合数C²n , 模型阶数迅速上升,致使Laplace 变换法运算量极大。另一方面,由于热参数固定,这种传统方法无法处理温度、老化与热模型参数的耦合作用,鲁棒性较差。

为此,有学者用Kalman 滤波去处理热模型结温求解。Kalman 滤波将损耗模型得出的实时结果作为输入,估测结温作为输出。Kalman 滤波的自适应特性允许在老化效应和可变工况条件下获得一致、准确的结温估计,增强了求解鲁棒性。同理, 采用扩展Kalman 滤波也可修正热模型参数,增强结温求解的鲁棒性。为减小计算负担,文献[21]将结–壳热模型限制为3 阶,将壳–散热模型限制为2阶,共有10 个模型参数。总而言之,Kalman 滤波类方法是增强结温估计鲁棒性的有效途径,但计算复杂度并未降低。

文献[22]中提出了三次迭代法求解结温。不同于大多数现有方法的单周期计算模式,三次迭代法利用多周期同一相对时刻的功率损耗与结温之间的耦合关系迭代计算,从而降低温度–损耗耦合效应产生的累积误差。但由于过度采样,该方法会进一步降低热模型法的计算速度和结温监测的实时性。

为了降低热模型法计算复杂度,文献[23]提出了低阶滤波法。采用低阶的无限冲击响应(infinite impulse response,IIR)数字滤波器可在维持一定结温估算精度的前提下减小计算复杂度。IRR 数字滤波器参数可通过成熟的Steiglitz-McBride 方法识别,对比其他方法更易于在现实数字系统中构建。

文献[24]提出了基于机器学习的结温求解方法并测试了支持向量机、随机森林、神经网络等回归算法的性能,然而该研究中的训练集数据均来自仿真,在实际应用中收集足够量的样本仍是一大难题。

事实上,尽管新模型和求解算法层出不穷,但均未从根本处理精度–计算复杂度间的矛盾。另一方面,热模型法多参低速的根本问题鲜有涉及、无法解决。下文将详细分析热模型法的优缺点。

1.1.6 热模型法的优缺点

热模型法具有以下两点优势:1)理论上可将芯片在多维度分割,近似获得温度场分布,便于热 应力分析,但大多数应用场景仅关注器件平均温度或最高温度,故该优势难以发挥;2)离线获取热模型参数后,侵入性较小,仅需电压电流测量计算损耗,无需改变被测器件的运行状态。

热模型法的缺点很明显,可概括如下:1)器件热暂态为s 级,远大于ns 秒级的电磁暂态,故响应速度极慢,对于运行工况复杂多变的变换器,监测结果无法跟随结温变化,不满足实时性要求,监测误差大,严重制约结温控制性能;2)建模过程参数获取难度大,高精度热模型通常包含几十甚至几百个热网络参数,全部需通过试验标定,耗时费力;3)功率器件损耗计算复杂,其中开关损耗计算涉及电压电流波形积分,故计算量极大;4)热 模型构建过程仅考虑热传导效应,忽略了辐射、对流效应,存在无法消除的系统误差;5)热网络参 数受目标器件老化影响严重,因此发展为CAE 结温监测方法的难度极大。

总体而言,热模型法多参低速问题限制了其在工业界的应用,故TSEP法成为主流SiC MOSFET结温监测方法。

1.2 基于热敏电参数的结温监测方法

针对热模型法的缺点,国内外学者提出了TSEP法,并逐渐成为主流结温监测方法。

1.2.1 TSEP 法的基本原理

功率器件中本征载流子浓度近似与结温呈指数关系,因此大部分电参数均与结温有关,被称为热敏电参数(TSEP)。通过离线标定得到TSEP-结温基准,可将结温监测问题转化为TSEP 在线测量问题。TSEP-结温基准是广义的,通常无法解析表示,仅能以表格形式给出其离散化的近似结果。对于标定未涉及基准,通常用插值、拟合等数学方法逼近。

TSEP法的极限结温监测精度取决于选用TSEP的灵敏度,即结温发生单位变化时TSEP 的变化量dTSEP/dTj。

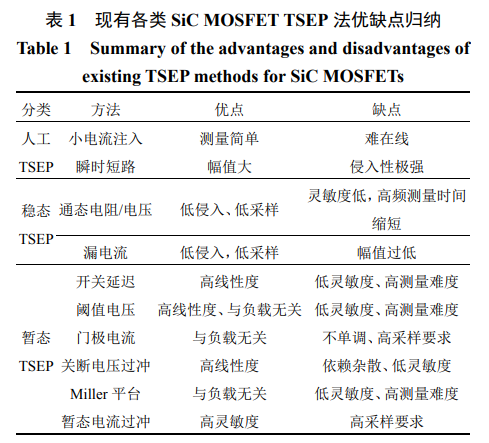

1.2.2 TSEP 法的分类

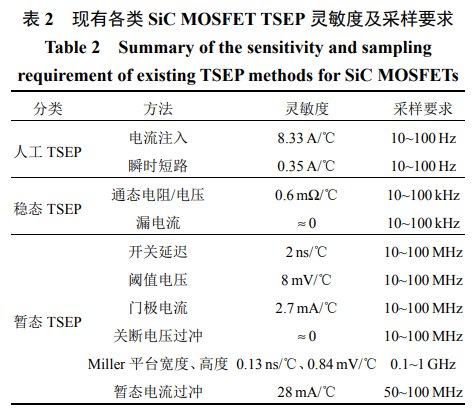

根据使用的TSEP 是否在功率器件内天然存在,TSEP 法可分为本征TSEP 法与人工TSEP 法。前者选用天然存在的TSEP,后者选用的TSEP需通过人工干预产生,如电流注入、制造瞬时短路等。人工TSEP 由于可控制激励条件,通常具 有较大的幅值与灵敏度。例如短路电流灵敏度高达8.33A/℃,远超大多数TSEP。此外,由于短路时间被控制在10~20s,对策略设备的采样率要求极 低,通常小于100Hz。但这类方法侵入性极强,对被测器件及变换器寿命负面影响大,实施成本高、 难度大。本征TSEP 法不需人工干预,故无此类问题,是目前主流的结温监测方法。本征TSEP 法根据参数产生时间可进一步分为稳态TSEP 法和暂态TSEP法。它们各具优势,是当前的研究热点。

1.2.3 稳态TSEP 法

稳态TSEP 法测量于器件的通态或阻态。由于器件稳态(约等于开关周期)远长于开关暂态(几十ns),这类TSEP 法对设备采样率要求相对较低,只需与开关频率匹配即可。最常用的稳态TSEP 是器件功率侧通态电阻或通态压降。由于电导调制效应,二极管、IGBT 等双极型或混合型器件的通态电阻随通态电流变化;作为单极型器件,SiC MOSFET 在线性工作区的通态电阻几乎不随通态电流变化。因此,通态压降法多用于IGBT,通态电阻法多用于SiC MOSFET。基于这两种参数的结温监测方法都需要测量目标器件的通态压降和通态电流,因而本质上是同种方法。在SiC MOSFET常见工作温度区间,载流子受晶格振动散射作用明显。随着结温上升,散射作用增强,迁移率下降导致电阻率上升。因此,通态电阻一般与结温呈正相关。

通态压降法的难点在于从数百V 高关断电压中提取数百mV 低通态压降,这往往需要特制的辅助测量电路。最早的通态压降测量电路诞生于20世纪 90 年代,其基本原理是利用二极管阻隔关断大电压,以维持测量端低压状态。二十年来,各种结构及原理的通态压降测量电路层出不穷,促使通态压降法成为应用最广的结温监测方法。然而,此类方法在SiC MOSFET 中的应用效果不尽人 意,原因如下:1)由于掺杂浓度更高,同容量SiC MOSFET的等温通态电阻仅为Si 基MOSFET的1/3,灵敏度极低,严重制约结温监测精度;2)更高的开关频率缩短了通态电阻的可测时间,对测量设备的带宽与采样频率要求增高。

另一种稳态TSEP 是器件阻态下功率侧的漏电流。Si 基IGBT的漏电流在100℃下达数mA, 可用于监测结温。然而,由于SiC MOSFET 阻断能力更强,其漏电流在100℃时仅为数μA,难以提取。因此,功率侧漏电流不适用于SiC MOSFET结温监测。

综上所述,SiC MOSFET 稳态TSEP 受限于低幅值与低灵敏度,结温监测精度较差。

1.2.4 暂态TSEP 法

SiC MOSFET 暂态TSEP 的种类多于稳态TSEP,具有灵敏度高、不受开关频率影响的优势, 根据产生时间可分为导通TSEP与关断TSEP。常见的暂态TSEP包括开关延迟、门极阈值电压、门极驱动电流、Miller平台、关断电压过冲、导通暂态电流过冲等。其中,与开关延迟和门极阈值电压有关的研究最为普遍。开关延迟包括器件的导通延迟和关断延迟,其与母线电压、门极电容、门极内阻及Miller 电容等多个参数均有关,而后3 个参数均随结温变化。

在以上参数的综合作用下,关断延迟通常与结温呈正相关,且线性度较高;导通延迟通常与结温呈负相关,且线性度也较高。开关延迟的高线性度可简化基准标定过程,但其缺陷更为明显:1)作为时间参数,开关延迟测量电路需要大量触发捕获、信号处理及逻辑运算环节,其复杂程度远高于其他暂态参数测量电路;2)SiC MOSFET的开关速度极快,开关暂态仅为 ns 级,使得开关延迟的灵敏度仅为ns/℃,从而限制结温监测精度。

门极阈值电压与门极电流均通过SiC MOSFET门极测量,受负载影响较小,监测结温鲁棒性强。 阈值电压通常定义为IGBT或MOSFET等功率器件导通瞬间的门极电压,对应于器件进入深耗尽(高频)或强反型(低频)的状态。由定义可知,在线测量阈值电压的难点在于准确判断器件导通。常见的导通判别方法包括捕捉法与扫描法。前者通过功率回路杂散电感产生的感应电压判断,易受电流振荡影响,误差较大;后者在门极电压超过特定值后发 出扫频信号判断器件是否导通,在线实施难度大、 成本高。总体而言,门极阈值电压的测量难度大, 且对结温的灵敏度不高。

SiC MOSFET 和IGBT同样作为压控器件,其门极电流仅在导通暂态产生。门极电流通过门极回路对栅源电容充电,抬高栅源电压,使器件导通,其峰值与门极内阻有关。门极内阻与器件结温呈正相关,但在封装内部无法直接测量。因此,门极内阻温变模型通常用门极电流峰值温变模型代替。 然而,门极电流峰值在部分功率器件中与结温呈正相关,在部分功率器件中与结温呈负相关。文献[51]提出SiC MOSFET的新型门极导通暂态模型,引入门极杂散电感,成功解释这一现象。同时表明,某些型号SiC MOSFET 门极峰值电流随结温变化可能不单调,而门极内阻的测量需要复杂的电路模型解算,因而限制了它们用于监测结温的性能。

有研究者指出IGBT 模块的关断电压过冲可反映芯片的结温。关断电压过冲产生于IGBT 关断时,迅速下降的电流−di/dt 在回路杂散电感Ls 上感应出的电压Lsdi/dt。IGBT 关断电压过冲与结温呈正相关,且线性度极高,其灵敏度正比于功率回路杂散电感。然而,SiC MOSFET 由于开关频率高, 其封装中的杂散电感通常低于IGBT,因此关断电压过冲的灵敏度降低。SiC MOSFET 模块和分立器件的关断电压过冲几乎不随结温变化。因此,关断电压过冲不适用于SiC MOSFET 结温监测。 Miller 平台指IGBT 或MOSFET 导通暂态,驱动电流全部用于门极电容充电而门极电压维持不变的阶段,其宽度及高度均可用于IGBT结温监测。一方面,Miller平台宽度的灵敏度极低, 仅为0.13ns/℃;Miller平台高度的灵敏度也仅为0.84mV/℃。另一方面,Miller平台的测量较为复杂,需要特制驱动电路以改造驱动电压波形,如延长饱和电压时间、增加脉冲数量等,对变换器运行负面影响较大。因此,Miller平台法并未从IGBT推广至SiC MOSFET。

清华大学张品佳团队在论证SiC MOSFET 体二极管区与通态电阻区等温性后,首次提出利用导通暂态电流过冲监测结温。暂态电流过冲本质为体二极管的反向恢复电流,取决于反向恢复电荷Qrr与电流变化率。由于Qrr高度依赖载流子的行为, 对温度呈极其敏感的双指数函数规律。因此,暂态电流过冲灵敏度高达28mA/℃,可提升结温监测精度。但该方法仅适用于无外加肖特基二极管的SiC MOSFET,且对测量设备采样率及带宽要求较高, 增加了监测成本。

上述各类TSEP 法的优缺点总结于表1,其中直接影响结温监测效果的灵敏度和采样频率要求见表2。灵敏度反映了对应TSEP 法的极限结温监测精度,采样频率要求则可一定程度反映方法成本。 由表2 可知,稳态TSEP 和暂态TSEP 特性迥异。

1.2.5 热敏光参数法

文献[56-57]发现,SiC MOSFET 的体二极管光辐射强度与结温有关,并基于此现象提出了热敏光参数(thermal sensitive optical parameter,TSOP)的概念。TSOP 随结温变化的原因是结温可影响电子与空穴的产生率及复合率,从而改变复合光谱。TSOP法不需要与目标器件产生电气接触,侵入性低,安全性很高。然而,功率器件的不透光封装会阻碍TSOP 的测量,导致TSOP 法难以实际应用。

1.2.6 TSEP 法的优势

TSEP 法具有以下显著优势:1)可在每个开关周期测量,具有高响应速度,响应时间在ms 级, 适用于复杂工况下的功率器件结温监测,有利于构建高动态性能结温控制系统;2)计算简单,通常仅需要一步映射即可得出结温;3)种类繁多,针对不同型号器件及应用场景,可选择最合适的TSEP;4)TSEP 法所需参数较少,利于发展CAE结温监测方法。基于以上原因,无论对于SiC MOSFET还是传统Si基器件,TSEP法都是主流结温监测方法。

1.2.7 TSEP 法的核心问题

SiC MOSFET作为新兴宽禁带器件代表,其结构、材料特性与Si 基IGBT迥然不同,相关TSEP结温监控理论技术面临挑战,存在以下突出问题:

1)多数TSEP 由Si 基IGBT 直接嫁接,底层机理不明,理论体系缺失。例如,许多TSEP 机理分析中认为载流子迁移率、扩散常数、扩散长度、 弛豫时间等参数与结温无关,但在通态电阻机理分析中却考虑了迁移率温变特性,从而使理论分析与通态电阻正温度系数的实验现象一致。事实上,载流子迁移率受多种散射机制影响,如晶格散射、Coulomb散射等,散射几率与结温息息相关。因此, 载流子迁移率随结温的变化规律较为复杂,在功率器件常见工作范围与结温呈负相关。根据Einstein关系,扩散常数、扩散长度、弛豫时间均与结温有 关。忽略迁移率的温变特性与物理事实严重不符, 导致理论体系不完备。

2)TSEP 机理错综复杂,分散性强,建模难度高,现有模型失准。例如,IEEE Fellow D. Lorenz.在其论文中提出SiC MOSFET 门极暂态电流峰值与结温呈正相关。IEEE Fellow M. Liserre 论文中的论述与之相反,认为与结温呈负相关。该分歧源自双方分别认为门极导通暂态模型的温变参数为门极内阻与栅源电容,其根本原因是现有SiC MOSFET 门极导通暂态模型失准,阻碍相关TSEP法的推广与发展。

3)受器件特性影响,TSEP 普遍灵敏度较低,制约结温监测精度。SiC MOSFET 属于宽禁带器件, 其非简并掺杂浓度远高于Si 基器件。一方面,这带来了高电导率、低暂态时间、高阻断电压等优良特性,促使其蓬勃发展。另一方面,高掺杂浓度限制了大部分TSEP 的灵敏度。例如,高电导率导致通态电阻灵敏度降低;短暂态导致开关延迟灵敏度降低;低杂散参数封装设计致使关断电压过冲灵敏度减低;高阻断能力使得漏电流幅值过低,无法用于结温监测。低灵敏度严重制约了结温监测精度,更多高灵敏度TSEP 亟待提出。

4)TSEP 法监测精度受器件老化影响严重,长期运行精度降低直至失效。因此,亟需发展CAE结温监测方法。

2 考虑老化影响的SiC MOSFET结温监测技术

CAE 结温监测方法由经典结温监测方法和老化补偿技术构成,其基础是器件老化对结温监测精度的影响分析。然而,结温与多模态老化对TSEP的影响存在强耦合关系,老化补偿难度极大。因此,大部分CAE 结温监测方法仍局限于周期性离线重标定的方式,其成本高,且不满足在线性的基本要求。发展CAE 结温监测方法已成为领域内重大挑战与公认难题。

2.1 SiC MOSFET老化对结温监测精度的影响

2.1.1 器件老化模式分类

SiC MOSFET老化根据发生位置分为封装老化与芯片老化。封装老化主要包括键合线老化、铝金属层重构、焊点及焊锡层退化;芯片老化主要包括门极氧化层退化与体二极管区双极性退化。热模型法精度受封装老化影响严重;绝大部分TSEP 法精度既受封装老化影响也受芯片老化影响。

2.1.2 封装老化对热模型法精度的影响

图5 为SiC MOSFET 典型封装结构示意图。 SiC MOSFET 自带体二极管(参考图6 中漏源间仅有的一个PN 结),因此无外加二极管芯片。SiC MOSFET 芯片与各个引脚通过键合线及焊点连接。

芯片与铜基板间有多层覆铜陶瓷板,并通过焊层固定,铜基板外通常装有散热片。芯片工作时,其产生的热量一般沿图5 所示方向传递。假设采用热模型法,观测点选于散热片外侧,则芯片与散热片间的热阻Rth,ja是关键参数。Rth,ja包含各封装层、焊锡层及铜板的热阻。由于各封装层的热膨胀系数不 同,热应力被转化为机械应力,引起焊锡层老化,直接表现为焊锡裂痕、间隙等局部老化缺陷,阻碍热量由芯片向基板传递,宏观表现为Rth,ja增大。 根据式(3),Rth,jc增大后,假设总损耗不变,芯片与环境温差将增大,故采用原热网络参数计算将导致结温监测结果偏小。随着焊锡层老化发展,结温监测误差越来越大,最终导致热模型法失效。由图3可知,高精度热模型分层较多,热网络参数众多而难以修正。因此,以热模型法为基础发展CAE 结温监测技术极为困难。

2.1.3 老化影响的基本TSEP——通态电阻与阈值电压

不同于热模型法,封装老化与芯片老化均影响TSEP法的精度,需分别分析。通态电阻(Rds,on)与阈值电压(VTH)是SiC MOSFET中最基本的TSEP,其 余TSEP 大多与它们相关。例如,开关延迟、Miller平台、暂态电流变化率与VTH有关,通态压降由Rds,on决定。因此,分析老化对 Rds,on与VTH的影响可在一定程度反映老化对其他TSEP 的影响。

2.1.4 芯片老化对阈值电压的影响

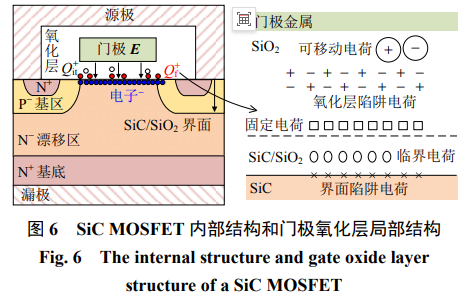

工业界使用的功率SiC MOSFET 一般为N 沟道增强型(具有正阈值电压且单一载流子为电子), 垂直结构。图6为典型SiC MOSFET 芯片内部结构和门极氧化层局部结构。

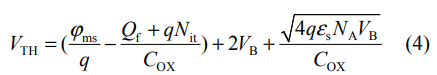

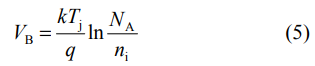

芯片老化影响VTH的原理如下。根据半导体物理,SiC MOSFET的阈值电压VTH可表示为

式中:q 为基本电荷量;Qf为固定电荷面密度;COX为氧化层比电容;NA为受主掺杂浓度;εs为SiC 介电常数;Nit 为界面陷阱电荷面浓度;ϕms 为金属半导体功函数差。VB为Fermi 电势差,可表示为

式中k 为Boltzmann 常数,本征载流子浓度ni 随结温上升呈指数急剧增大。因此,VB整体与结温呈负相关。根据式(4),VTH 也与结温呈负相关,并可作为SiC MOSFET 结温监测指标。然而,当门极氧化层发生老化时,VTH随之偏移,其原理如下。

在SiC MOSFET 的门极存在MOS 结构,如图6 所示。为使器件导通,门–源极间需施加正偏电压vgs,从而在氧化层中形成垂直电场E。该原理可类比平行板电容,驱动N−区电子向门极漂移,同时P 区空穴远离门极漂移。最终,电子在SiO2/SiC界面附近积累,形成强反型层即沟道,连通 N+区和N− 漂移区,使得漏源间形成通路,器件进入通态。 当施加漏源电压,电子从源极沿沟道漂移至漏极形成电流。然而,在电热应力作用下,一部分高能电子在界面被陷阱电荷俘获致使Nit 减小。根据式(4), 一旦陷阱电荷数减少,VTH 将正向偏移。这种现象被称为MOSFET的正偏压温度不稳定性 (positive bias temperature instability,PBTI)。在撤去电热应力后静置器件,部分陷阱电荷可能释放电 子,VTH部分恢复,但持续应力会导致不可逆结果, 产生氧化层老化。

此外,SiC MOSFET作为宽禁带器件,SiO2 与SiC之间的隧穿势垒低于Si 基器件。因此,高能电子更易越过势垒抵达SiO2层,从而在高电热应力下形成Fowler-Nordheim(FN)隧穿电流。FN 电流会破坏Si—O 键并产生更多缺陷,从而增大门极漏电流。这种情况下,MOS 结构不再等价为平行板电容,还应考虑其漏阻承压,阈值电压随之增大。

总而言之,PBTI 效应和FN 漏电流均会导致阈值电压在SiC MOSFET 长期运行中增大,即阈值电压与芯片老化程度呈正相关。

2.1.5 封装老化对阈值电压的影响

最新研究表明,虽然芯片老化对VTH的影响起主导作用,但封装老化对VTH也会产生一定影响。 究其原因,SiC MOSFET的门极杂散电阻随封装老化而增大,因而分压增加并导致VTH增大。然而, 这一效应作用较小因而被大多数研究者忽略。

2.1.6 封装老化对通态电阻的影响

封装老化对Rds,on 的作用原理如下。根据图7所示的SiC MOSFET封装连接,Rds,on 包括封装电阻RPack 与芯片电阻RChip。RPack 包括键合线电阻RBW,焊锡层电阻RDAS 以及焊点电阻RSJ。热应力会导致焊锡退化与键合线老化。焊锡层及焊点的老化缺陷会引起RDAS与RSJ 增加。键合线老化出现的开裂、间隙等缺陷会导致RBW增大。因此,Rds,on 正相关于封装老化程度。

2.1.7 芯片老化对通态电阻的影响

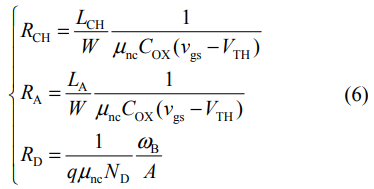

芯片老化会导致RChip增加,主要包括漂移区电阻RD、沟道电阻RCH以及积累层电阻RA 。以上电阻成分可分别表示为

式中:LCH为沟道长度;LA为积累层长度;μnc为电子电导有效迁移率;ND为漂移区施主掺杂浓度;W为芯片胞体长度;ωB为漂移区厚度;A 为芯片电流 截面积。由式(6)可知,RCH、RA均与VTH有关。因此,当VTH随门极老化增大时,RCH、RA也会增大。 此外,SiC MOSFET的体二极管区在电热应力下可能发生堆垛层错或基平面位错等晶格缺陷,引起双极性退化,导致RD增大。由上述分析可知,Rds,on与封装老化程度及芯片老化程度均呈正相关。当功率器件老化发展,通态电阻法误差增大,直至失效。

由以上分析可知,绝大多数TSEP 都与Rds,on或VTH有关,因而均会受到器件老化的影响。相比之下,门极内阻Rg,int 是为数不多的与Rds,on 或VTH无关的TSEP。然而,Rg,int 包含门极回路的键合线电阻,因此也随封装老化发展而增大。

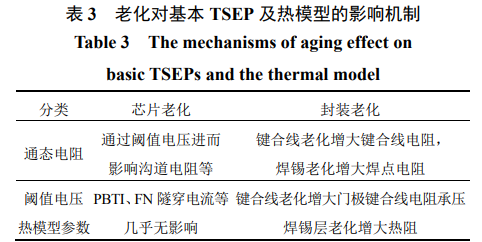

上述老化对基本TSEP 及热模型的影响机制归纳于表3。可见,多模态老化与结温对热网络参数和TSEP 的影响呈现强耦合,发展CAE 结温监测方法难度极大。

2.2 SiC MOSFET 考虑老化影响的结温监测方法

2.2.1 CAE 结温监测方法

热模型法参数众多、测量复杂,逐一修正补偿繁琐,不利于发展CAE 结温监测方法。尽管TSEP法参数少,目前大部分方法也未考虑老化影响,属于经典方法范畴。分析TSEP 法精度时,通常默认目标器件老化程度与标定时接近,缺少有效老化补偿方法。

有研究指出,在SiC MOSFET 门极加负向偏置电压能恢复VTH 的PBTI 偏移,从而降低氧化层老化对结温监测精度的影响。然而,PBTI 仅可实现部分恢复,且该方法无法消除封装老化的影响。 文献[75]提出,利用Rds,on监测SiC MOSFET结温时,加入体二极管通态压降vF,可消除PBTI 对结温监测的影响。然而,测量vF需以离线方式注入小电流, 难以与结温监控结合,且该方法无法消除封装老化的影响。文献[76-77]提出,可在通态电阻法基础上引入Rth,ja间歇性测量,从而消除封装老化的影响, 然而,此方法未考虑芯片老化的影响,且Rth,ja的测量较为繁琐。文献[78]首次利用多个TSEP 及机器学习方法将老化与结温的作用解构,从而实现独立老化评估与结温监测,然而,此方法将所有的老化模态统一量化为功率循环次数,缺少不同机理、 位置、时间尺度的老化影响分析。

功率器件运行一定时间后重新标定TSEP-结温基准是普适性最强的CAE 结温监测方法,被称为周期性重标定法。然而,重标定成本高,执行时间长,不仅缺乏指标判断何时应摒弃原有基准,还会使在线监测方法退化为离线方式。文献[80]提出χ消去法以减小杂散参数变化对结温监测的影响, 然而,此方法仅适用于变换器应用场景改变引起的杂散参数变化,未考虑器件老化影响。

2.2.2 CAE 结温监测方法的关键问题

总体而言,CAE 结温监测方法仍处于发展初期,面临两个核心问题:

1)SiC MOSFET 老化机理错综复杂,TSEP 老化温变模型缺失,难以支持老化补偿技术。现有TSEP温变模型仅将结温作为唯一输入变量,缺少老化后模型的变化分析,老化影响研究过度依赖加速老化试验。事实上,在老化温变模型中,老化与结温的作用同等重要。

2)SiC MOSFET 多模态老化与结温对TSEP的影响呈现强耦合,在线老化补偿难。耦合效应使得任意TSEP 或热网络参数均为老化、结温的多元函数,破坏了温变模型中TSEP 与结温的双射关系, 使结温监测技术失去立足之本。在上述机制下,根据单TSEP 难以提供结温信息,而引入多元特征增加了方法复杂度和测量成本,降低了可行性。周期性重标定方案可行性强,但不满足在线性与实时性的基本要求。

3 结温控制方法

SiC MOSFET 结温控制是结温监测的重要目的,也是提高变换器可靠性、维持健康状态及延长使用寿命的直接手段,又称为主动热管理技术(active thermal management,ATM)。结温控制技术在各类型功率器件中差别不大,在此一并介绍。根据控制目的和应用对象不同,可大致分为结温均衡控制和结温平滑控制技术。这两类技术的实现方法相对统一,本文一并讨论。首先分析结温均衡与结温平滑的意义。

3.1 结温均衡控制的意义

结温均衡控制的目是使得变换器运行时内部器件结温趋于一致,从而均衡器件老化发展速度,延长变换器预期寿命。下文以两电平变换器桥臂为例,通过简单的数学分析阐释结温均衡的意义。

假设上桥臂MU 的失效率为λU,预期寿命为RU;下桥臂ML失效率为λL,预期寿命为RL。显然,单位时间上/下桥臂不失效的概率分别为1−λU 和1−λL。桥臂不失效的概率Pre为上/下桥臂均不失效的概率,即Pre=(1−λU)(1−λL)。因此,桥臂的总失效率λa为:λa=1−Pre=λU+λL−λUλL。

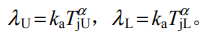

显然,λU、λL与结温均呈正相关。不失一般性, 假设λU、λL表示为:

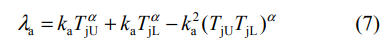

其中:ka 和α 均为正系数;TjU 为上桥臂结温;TjL 为下桥臂结温。可计算λa为

假设桥臂结温均衡分布时,上/下桥臂结温均为Tjb。上/下桥臂器件初始参数不同导致老化速度不同,老化快的器件通态电阻大、损耗大,因而结温高。假设上桥臂比Tjb 高δx,下桥臂比Tjb 低δx,即TjU=Tjb+δx,TjL=Tjb−δx。Tjb 可超过100℃,而δx通常小于10℃。因此,δx/Tjb 是一个较小量,代入式(7)并做一阶泰勒(Taylor)展开近似得:

根据式(8),桥臂总失效率λa 为δx 的单调增函数,当δx 为0 时λa 最小。通过上述分析可知,当桥臂温差为0,整体可靠性最高。这一结论可推广到多桥臂或多个功率器件的串联结构。

桥臂的预期寿命Ra 可根据短板效应得出:Ra=min{RU,RL}。桥臂均温后,原本高温的器件寿命延长,原本低温的器件寿命缩短。但由于Ra取决于寿命较短的器件,因此桥臂均温后Ra增大。可见, 结温均衡控制对降低变换器总体失效率,提高其可靠性有重要意义。

3.2 结温平滑控制的意义

结温平滑控制与结温均衡控制均为提高变换器可靠性的重要手段。结温均衡控制关注变换器内多个器件结温分布的一致性,提升桥臂和变换器整体的可靠性及预期寿命。对于单体器件,高温器件结温降低,可靠性提升;低温器件结温升高,可靠性反而降低。换言之,结温均衡控制无法提高所有器件的可靠性。在部分变换器中,核心功率器件较少,结温均衡控制的效果有限。结温平滑控制关注单体器件的结温波动,可弥补结温均衡控制的不足。日本学者研究表明:结温波动幅值每增加20℃, 功率器件键合线寿命降低90%,足见结温平滑控制的重要意义。

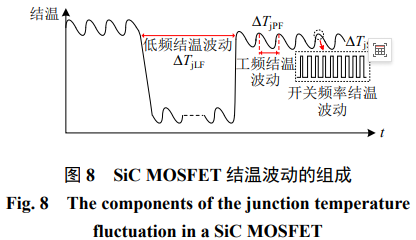

变换器运行时,SiC MOSFET 的实际结温波动通常由多种频率的结温波动叠加而成,如图8 所示。 其中,低频结温波动 ΔTjLF、工频结温波动 ΔTjPF 与开关频率结温波动 ΔTjSF 是最主要的成分。ΔTjSF 由器件的开关动作产生。器件导通结温上升,器件关断结温下降。因此,ΔTjSF的频率通常接近开关频率。 然而,ΔTjSF 的幅值相对较小,一般忽略其对器件寿命和可靠性的影响。另一方面,只要器件正常工作,ΔTjSF 就无法避免,结温平滑难度极大。ΔTjPF 由负载电流正弦波动引起,其频率一般接近工频。ΔTjLF由环境温度变化或负载改变引起,其频率较低且不固定,但波动幅值较大。对于我国电网 50Hz 的工频,ΔTjPF 对功率器件寿命的影响不及 ΔTjLF ;但对于一些基频较低的情况,ΔTjPF对器件可靠性和寿命的影响可与 ΔTjLF 相比。因此,结温波动抑制的首要目标一般是减小低频结温波动对器件寿命和可靠性的影响。

3.3 结温控制的原理

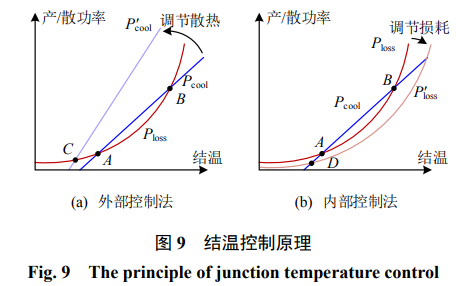

结温均衡及平滑控制技术根据调控对象可分为内部控制法和外部控制法。前者通过调节器件的总损耗控制结温,后者通过调节器件的散热条件控制结温。这两类结温控制方法的原理如图9 所示。

SiC MOSFET 的产热功率(总损耗Ploss)与结温的关系近似为二次函数。假设器件散热条件良好,环境温度稳定为Ta,则其散热功率Pcool 可表示为:Pcool=(Tj−Ta)/Rth,ja 。 显然,Pcool是一条斜率为Tj/Rth,ja、截距为−Ta/Rth,ja 的直线。产热曲线与散热曲线通常有两个交点 A、B。A 点附近结温受到正向 扰动时上升,散热功率将超过产热功率,结温下降。 相反,当结温受到负向扰动时,散热功率将小于产热功率,结温回升。可见,A 点是一个散热–产热稳 定平衡点,存在负反馈机制。同理,可证明B 点是不稳定平衡点。当结温升至B 点右侧,将进入正反馈,结温激增导致器件热击穿。

假设控温目标是降低结温,外部控制的方式为提高散热能力(减小Rth,ja),Pcool曲线移动至P’cool与产热曲线交于C 点(见图9(a));内部控制的方式为降低器件损耗,Ploss 曲线移动至P’loss与散热曲线交于D 点(见图9(b))。显然C 和D 点对应结温低于A点,控温目标达成。

一般而言,散热条件固定,因而从器件层面降低损耗是主流的降温方式。器件损耗包括开关损耗Psw和通态损耗Pos。其中,开关损耗产生于器件导通或关断暂态,正比于开关频率,还与开关速度、 负载电流、母线电压等因素息息相关的。在变换器工况无法调节情况下,适当调低开关频率、增大驱动电阻以加快开关速度或采用软开关技术是减小开关损耗的主要方式。在器件制备层面,也可以通过减少载流子的弛豫时间加快开关速度以降低开关损耗。器件的通态损耗主要取决于负载电流及通态电阻。在变换器工况一定条件下,减小通态电阻 是降低通态损耗的唯一途径。减小通态电阻的方法较多,驱动层面可提高电平,器件制备层面可降低阈值电压、提高载流子浓度及材料电导率。此外, 对于反向通态,还可以调节续流二极管的通态时间以减小损耗。

3.4 内部控制法

内部控制法是主流结温控制方法。其基本逻辑为需要提高结温时增加损耗,需降低结温时减少损耗。多数内部控制法通过调节开关损耗控制结温。 文献[85-86]提出通过改变驱动阻尼电路中的吸收电容调节开关损耗以控制结温。吸收电容越大,开关损耗越低;文献[87]设计了一种由多个定值电阻并联而成的可调门极驱动电阻,通过改变阻值调节开关损耗以控制结温,驱动电阻越大,开关速率越慢,开关损耗越大;文献[88]在此基础上设计了可连续调节阻值的等效驱动电阻器,省去了多余定值电阻。此外,改变门极驱动电平调节通态损耗也可控制结温,驱动电平越高,通态电阻越小,通态损耗越小。以上方法都归为基于驱动参数调节的内部控制法。此类方法需要额外硬件、成本高,通常用于单体器件,而无法大规模应用于变换器。该方法的另一个缺陷是侵入性强,影响变换器性能。

另一类内部控制法不需要增加额外硬件。其中,最常用的方法是调节开关频率。器件开关损耗Psw正比于开关频率fsw。为减小结温波动幅值,需降低结温时可调低fsw,需提升结温时可调高fsw。 然而,降低fsw 会影响变换器的输出电能质量,增大总谐波畸变率(total harmonic distortion,THD)与电压纹波系数。若变换器的负载为电机,改变fsw还会增大转矩脉动。为此,有研究者尝试在控制算法内增加约束以减小调节 fsw 对负载电机转矩的影响。然而,此方法的代价是降低了变换器7%的效率,难以满足实际需求。文献[96]尝试减小调节fsw对变换器输出电流THD 的影响,但未考虑对变换器效率的影响。总体而言,通过调节fsw 控制结温虽简单直接、不需额外硬件,但对变换器运行负面影响极大。

为了降低结温控制对变换器的影响,非侵入式的内部控制法已成为趋势。文献[97-98]提出通过调节死区改变器件通态损耗以控制结温,然而,此方法仅适用于Si/SiC 混合器件,应用面较窄;文献[99]提出通过调节 SiC MOSFET 导通延迟时间改变体二极管区的通态损害以控制结温。该方法对THD的影响低于传统开关频率法,但仅适用于有反向电流的工况;文献[100]提出基于混合调制的结温均衡方法,通过改变调制策略自适应调节桥臂温差,该方法对变换器效率及THD 几乎无影响,但却无法均衡不同桥臂的器件结温。综上,降低结温控制对变换器性能的影响必然伴随成本增加、适用范围缩小等问题。追寻它们的平衡仍是未来内部控制法的发展方向。

3.5 外部控制法

基于散热调节的结温控制方法(外部控制法)相对冷门。最典型的此类方法是通过改变散热风扇转速或冷却剂流量调节结温。二者本质是同一类方法,因为风扇转速改变的是空气冷却剂流量。 当结温上升时,加大冷却剂流量,反之则减小冷却剂流量。

然而,外部控制法存在如下两个重大缺点:1)响应速度慢,功率器件的热暂态持续时间远长于电磁暂态,因此,通过改变外部散热控制结温所需时间较长,失去TSEP 法的高响应速度优势; 2)目标器件平均结温上升。显然,散热功率始终维持最大时目标器件平均结温最低,一旦改变散热条件,目标器件平均结温必然升高。根据CMA 模型, 平均结温升高会降低器件可靠性与预期寿命。此外,有研究者提出改变器件的封装结构、内部材料以降低其热应力。然而,这类方法属于器件设计而非结温监控技术。前者关注生产过程中的器件,后者关注已投入应用的器件。

3.6 结温控制方法关键问题

现存结温控制方法代价较大,体现在两个层面:1)缺少与控制匹配的变换器级结温监测方法,导致成本高。变换器通常包含多个目标器件,它们的结温信息均需反馈给控制器。现有结温监测方法仅针对单体器件,需为每个器件配置独 立测量电路与信号处理电路。这种方式成本高、集成难度大,甚至需要调整变换器结构。2)调控量与工况指标高度相关导致控制方法侵入性强,对变换器性能负面影响大。门极参数、开关频率与变换器工况指标高度相关,调节它们对变换器输出电能质量和效率影响大。非侵入式的结温控制方法虽在兴起,但总体而言适用面较窄。

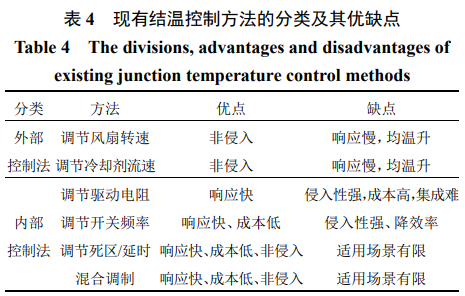

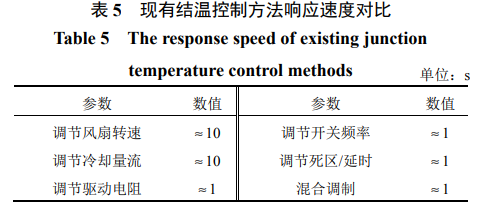

现有结温控制方法的分类及其优缺点见表4, 其中重要的量化指标见表5—7。响应速度反映了结温控制方法的动态性能,对效率和THD 的影响则体现了方法的侵入性。

4 SiC MOSFET 结温监控技术发展趋势和未来展望

SiC MOSFET 作为新兴器件,其结构、材料特性与Si 基IGBT 迥然不同,结温监控技术仍处于发展初期。为了提高SiC MOSFET 的可靠性并延长使用寿命,其结温监控技术需进一步在精度、成本、侵入性、可行性等方面做出改善。综合已有研究,未来发展方向可归纳如下:

1)深入研究TSEP 的温变机理及模型。TSEP法的温变机理与建模是指导TSEP 法标定、确保普适性的基础,也是分析其灵敏度的重要手段。然而,现有大部分TSEP 法机理分析较浅, 局限于定性分析TSEP 随结温的变化规律,标定基准过度依赖于试验结果而缺少理论指导。一方面, 这种研究模式难以确保TSEP 法在不同型号SiC MOSFET上的泛用性;另一方面,研究者忽略半导体物理底层理论,分析欠缺统一性与完备性。一个典型例子是,载流子迁移率、暂态寿命等参数的温变规律在不同研究里莫衷一是,解析描述大相径庭。长此以往,TSEP 法的提出易退化为实验–拟合–实验的周期性重复,从而在不同型号、厂家的器件间产生高壁垒,阻碍方法应用推广。因此,深入研究SiC MOSFET TSEP 底层机理,统一常用参数温变模型意义重大。

2)深入研究多模态老化影响机理及补偿方法。 SiC MOSFET 在长期运行中,遭受多场复合应力,退化机理复杂,多时空分布,且各个模态同步发生。然而,现有的CAE 结温监测方法仅关注其中的单种老化模态。例如,文献[108]通过引入门极电容充电时间这一参数消除门极老化的影响,但无法处理封装老化的影响。因此,研究多模态老化影响机理及对应补偿方法仍是功率器件结温监控领域的公认挑战。

3)发展精度与成本均衡的结温监测策略。

作为主流结温监测方法,TSEP法的精度上限取决于其灵敏度。总体而言,稳态TSEP 灵敏度低于暂态TSEP。然而,暂态TSEP的测量成本高, 通常需要高频、高带宽采样电路及对应的信号处理系统。部分暂态TSEP 法还依赖于特定信号触发及瞬时捕获,电路构造繁杂,成本昂贵。目前研究尚 未提出结温监测精度带来的收益与监测成本间的均衡策略。目前尚未有结温监测精度与监测成本间的均衡策略。简言之,对于失效风险较高、器件成本较高的应用场景,可提高TSEP 法的预算成本, 采用高精度的暂态TSEP 法;对于失效风险较低、 器件成本低的应用场景,更倾向于采用低成本的监测方法,如通态电阻法。TSEP 法种类繁多,缺乏此类均衡策略可能给实际应用带来困难。

4)发展性能与侵入性均衡的结温控制策略。

结温控制方法的性能与其侵入性间存在明显制约关系。一般而言,侵入性越强的方法,其控温效果越直接,可调范围越广,但对变换器的影响更大;侵入性较低的方法由于调控方案受限,其可调范围通常较窄,且适用场景有限。因此,对于一些可靠性要求高,但变换器效率要求较低的场景,可采用高侵入性方法;反之宜采用低侵入性方法。发展控制性能–侵入性均衡的策略对结温控制方法实际应用可起到重要推动作用。

5)发展结温与变换器性能协同优化控制方法。

结温控制并不是变换器运行的唯一优化目标。 对于多电平变换器,还需开展环流抑制控制、中点电位控制、多体器件电压均衡控制等。这些优化控制方法势必相互影响,且难以同时进行。现有研究仅关注单一目标,实际应用可行性较低。因此,亟需发展结温–变换器性能协同优化控制方法。

5 结论

发展SiC MOSFET 结温监控方法不仅符合宽禁带器件蓬勃发展的需求,还对提高我国未来电力系统可靠性具有重要意义。本文详细介绍了SiC MOSFET 结温监控方法研究现状,并将其分为经典结温监测、CAE 结温监测、结温控制3 个部分。对于经典结温监测方法,重点介绍了热模型法和TSEP法的原理、发展、分类及各自优劣,指出现有方法精度–成本亟待均衡、温变模型失准、老化机 理研究不足等关键问题。对于CAE 结温监测方法, 重点分析了器件多种老化机制对结温监测精度的影响,指出现有的老化补偿技术成本高、模型缺失、 局限于离线重标定等不足。对于结温控制方法,重点分析了结温均衡与结温平滑两类技术的意义、原理,介绍了主要方法及各自优劣,指出现有方法性能–侵入性亟待均衡,与其他优化控制难以协同等关键问题。最后,综合该领域的研究现状和归纳的关键问题,指出了SiC MOSFET 结温监控方法的未来发展方向。