文章来源:中国电机工程学报

作者:党子越,彭晗*,彭皓,康勇(强电磁工程与新技术国家重点实验室(华中科技大学电气与电子工程学院)

摘要:为了保障碳化硅(silicon carbide,SiC)在发生短路故障时可安全可靠的关断,需在掌握其短路特性基本规律的前提下,针对 SiC 短路耐受时间较短、短路下器件漏源极电压拐点不明显等特征,展开去饱和保护电路(desaturation faultprotection,DESAT)电路中关键参数的研究,并制定其工程化设计的参考标准。在此基础上,文中进一步提出基于氮化镓(gallium nitride,GaN)的高速、低传输延时的 DESAT 短路保护电路,短路保护电路的驱动动作延时仅为常规基于硅器件 DESAT 电路的 23.2%。所提出的氮化镓 DESAT 电路为 SiC MOSFET 短路保护电路的更优越的实现方案。

关键词:碳化硅;短路特性;DESAT 保护电路;氮化镓

0 引言

碳化硅(silicon carbide,SiC)具有更宽的禁带宽度、更高的击穿电场、更高的热导率和更高的电子饱和速率。相较于常规高压大功率硅基功率器件(insulated gate bipolar transistor,IGBT),SiC 更加适应于高压、高温、高频和高可靠性等应用领域。SiC 功率器件正在逐步应用于包括柔性直流输电换流阀、灵活交流输电装置、高压直流断路器、电力电子变压器等装置中。未来更高电压、更大容量和更低损耗的柔性输变电将对万伏级的高压大容量SiC 功率器件有更大的需求。

SiC 的安全可靠运行是其大规模应用的重要前提。由于芯片面积小、电流密度高的特点,SiC的短路能力较弱,主要体现在:短路耐受时间短和温度上升速率快。另外 SiC 在高速开关过程中,会通过器件和回路中的寄生电容产生高频耦合电流(Cpardv/dt),造成短路故障的误触发,并导致功率器件的误关断。这些均对 SiC 的短路保护电路提出了更高的要求,即准确捕获短路故障,并且快速关断功率器件。去饱和保护电路 (desaturation faultprotection,DESAT)为最为典型的短路保护电路,一般集成于功率器件的驱动芯片内。现有驱动芯片中 DESAT 参数大多围绕 Si IGBT 器件设计。然而SiC MOSFET 和 Si IGBT 在短路特性上存在明显差异:Si IGBT 的短路耐受时间约为 SiC MOSFET 的两倍,且短路时具有明显的导通压降拐点。

因而,Si IGBT 对于短路响应速率的要求低于 SiC MOSFET,且 DESAT 电路中阈值电压更容易确定。若将 Si IGBT 的 DESAT 电路直接应用于 SiC MOSFET,会导致器件因动作时间过长而损坏,以及因判断不准确而误关断等问题。

针对现工业界尚未存在成熟的 SiC MOSFET的 DESAT 短路保护电路的设计,本文深入分析DESAT 电路应用于 SiC MOSFET 短路保护中的关键参数。在此基础上,提出基于氮化镓(galliumnitride,GaN)的 DESAT 电压源保护电路,通过 GaN的高速开关特性和较强的电流能力,实现了超低的响应延时。所设计的 GaN 的 DESAT 可以配合常规SiC 驱动使用,可以应用于 SiC 的谐振驱动中。本工作不仅为研究人员设计 DESAT 保护电路提供了理论和工程指导,也提供了一种更加高速和小型化的 SiC MOSFET 短路保护的解决方案。

1 DESAT 短路保护电路

短路保护电路要求具有高可靠性、低损耗、低成本及避免过保护和欠保护等特点。DESAT 是最为成熟的短路保护电路,本章节将从 SiC MOSFET 的特性出发,针对 DESAT 电路的基本结构和关键参数的设计展开分析与阐述。

1.1 基本结构

DESAT 电路利用功率器件在常规工作与短路故障下采样电容两端的不同电压,在发生短路故障时通过关断驱动信号,实现器件的故障保护。其基本原理为:当功率器件导通时,其漏源极两端电压较低,DESAT 二极管导通,采样电容 Cbl 两端电压等于功率器件漏源极两端电压。若功率器件发生短路,功率回路中电流急剧升高,功率器件漏源极电压也相应抬升,DESAT 二极管截至,DESAT 电路对采样电容 Cbl 开始充电。当 Cbl 电压上升至参考电压时,DESAT 电路输出故障信号,关断功率器件。根据采样电容 Cbl 的充电方式,DESAT 电路可分为电压源型和电流源型。

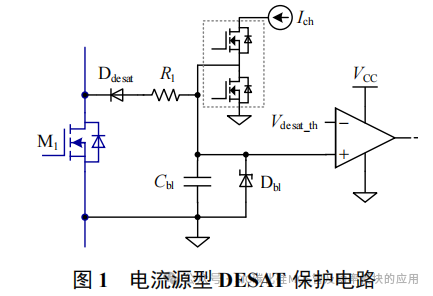

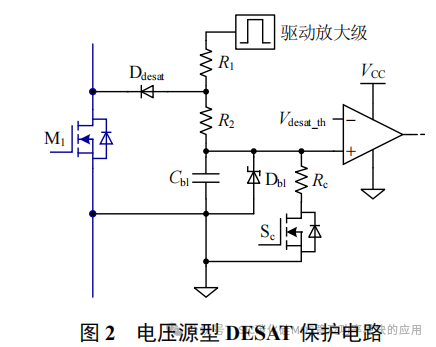

图 1 为一个典型的电流源型 DESAT 保护电路。电流源 Ich 通过半桥器件对采样电容 Cbl 进行充放电。Cbl 的充电时间由电流源决定:

R1 用来抑制功率器件关断时 dv/dt 所造成的干扰。半桥电路的控制信号与驱动信号相同。半桥电路的下管在器件关断时开通,构成 Cbl 的放电回路,也为功率器件的 dv/dt 通过二极管结电容串入的干扰电流提供低阻旁路。电流源型 DESAT 保护电路因结构简单、集成度高等特点,广泛应用于商用驱动芯片中。

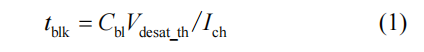

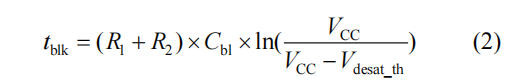

电压源型 DESAT 保护电路可有效提高采样电容的充电能力,进而提升短路保护的响应速度。该电路可利用驱动放大级对采样电容进行充电,不需要额外的充/放电回路,其基本结构如图 2 所示,其中:R1 一般较大,以保证较低的静态损耗;R2用于抑制功率器件关断时 dv/dt 引入的干扰。在实际设计中 R2一般远小于 R1。

若采样电容 Cbl 通过 R1 和驱动放大级进行放电,会因放电回路阻抗大,存在放电速率慢,保护误触发的风险。因而,在设计中加入由开关 Sc构成的低阻高速放电回路。电压源型 DESAT 保护电路中采样电容 Cbl 的充电时间由驱动电源、R1、R2、Cbl 所组成的网络决定,即:

式中 VCC为驱动电压。由此可见,可以通过合理设计 RC 时间常数,实现高速充电,极大提高短路故障响应时间。由于电压源型 DESAT 电路结构简单且充电时间可控的优点,电压源型 DESAT 常用于非芯片内集成的短路保护电路中。

1.2 阈值电压设计

阈值电压是 DESAT 保护的动作参考电压。阈值电压决定了 DESAT 保护动作时,功率器件短路电流的大小,是关系到能否安全关断器件以及是否存在过保护问题的关键参数。DESAT 保护阈值电压(Vdesat_th)等于二极管正向导通压降(VF),与功率器件在短路故障时漏源极电压(Vds_sc)之和,即:

SiC MOSFET 的 Vds_th 取值主要有两种方案:短路电流阈值法和功率耗散法。

1.2.1 短路电流阈值法

短路电流阈值法的基本思路是通过确定短路电流值,获取所对应的 DESAT 动作电压阈值。短路电流峰值约为最大稳态电流的 5~7 倍。在实际工程应用上,一般选择短路电流为最大稳态电流的 1.5~2 倍。在确定短路电流的基础上,可通过以下两种方法将短路电流转化为短路动作电压阈值,分别为:基于器件输出曲线的 I–V 曲线法和基于器件导通压降法。

1)I–V 曲线法。

在得到短路电流阈值后,可通过相应温度下的器件输出特性曲线,获得相应电流下的 Vds_sc。如文献中取电流阈值为 60A,在 25℃输出特性曲线上,依据栅源极电压为 20V,可读出所对应的 Vds_sc为 7V。

2)导通压降法。

将短路电流阈值乘以功率器件数据手册中提供的器件导通电阻(Rds_on)的典型值,即得到相应电流下的导通压降(Vds_sc):

然而 SiC MOSFET 的导通电阻随结温升高而升高。因而,在实际工作环境中(器件结温大于25℃),DESAT 电路会在低于短路阈值电流时保护动作。

1.2.2 功率耗散法

为了确保器件的安全关断,发生短路故障时器件上的功率耗散应小于其可承受的最大值。因此,功率耗散法是通过器件可承受的最大壳温(Tc_max),选择最大耗散功率(Pd_max),再基于相应驱动电压下的器件 I–V 特性曲线,确定 Pd_max 对应的短路电流与漏源极电压,满足:

然而,由于功率耗散的曲线是依据器件稳态连续工作下的损耗和温度变化特性总结出来的。而短路故障为单个脉冲故障,因而通过最大功率耗散得到的阈值电压相比短路电流阈值方案更为保守,可能会造成过保护问题。

综上,相比短路电流阈值–导通压降法与功率耗散法,短路电流阈值–I–V 曲线法通过选择合适结温下的器件输出特性曲线,得到对应短路电流下的DESAT 阈值电压是工程应用上更为合理的方法。

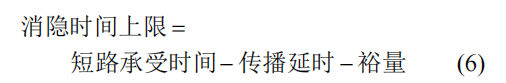

1.3 消隐时间设计

消隐时间代表采样电容的充电时间(tblk),是DESAT 电路的最短动作时间,也是保障 DESAT 电路正常工作所必要的间隔时间。tblk 过短会导致因 DESAT 采样电容在功率器件开关瞬态过程中的快速充电触发保护动作,造成功率器件的误关断。若 tblk 过长,DESAT 电路的动作时间超过功率器件短路的承受时间,将导致器件损坏。通常消隐时间设置的下限范围为 1.2~2 倍的功率器件开通时间。消隐时间设置的上限范围由功率器件的短路承受时间和 DESAT 传播延时决定,并留有一定裕量,即:

其中,功率器件的短路承受时间与功率器件特性和实际工作环境有关。文献中的 SiC 短路测试环境一般较为理想,无法完全反映功率器件在实际工作条件下的短路特性。DESAT 的传播延时为电容电压达到阈值电压后驱动输出由高变低的间隔时间。

根据现有 DESAT 芯片中的数据,传播延时一般为200ns。传播延时越小,短路保护的响应时间就越快,对于功率器件短路故障的保护就越及时,可更好的避免器件在短路故障下的性能失效。由此可见,DESAT 电路的传播延时直接影响功率器件短路故障时的响应速度。DESAT 电路消隐时间确定后,可根据式(1)或(2)进行 DESAT 电路相应的选型设计。

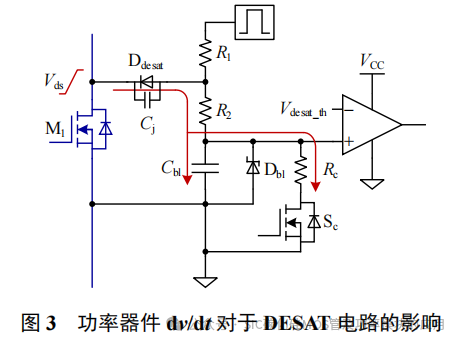

1.4 抗干扰特性

功率器件关断时的电压的快速变化(dv/dt)会通过二极管 Ddesat的结电容,对采样电容 Cbl进行充电,如图 3 所示。若该电流过大,采样电容电压两端电压会达到阈值电压,导致 DESAT 的误动作,造成功率器件误关断。由于 SiC 器件的 dv/dt 高达30V/ns,DESAT 电路中抑制功率器件 dv/dt 干扰尤为重要。干扰抑制的设计原则包括:

1)选取结电容小的二极管 Ddesat。

2)提供低阻抗放电回路,旁路 dv/dt 引入的干扰电流。

3)抑制充电电容在干扰下的电压峰值。回路中寄生电感在干扰下会与采样电容发生振荡,抑制充电电容电压振荡,一定程度上可避免电压达到阈值电压。

抑制 dv/dt 干扰的具体实现方法包括:

1)通过串联多个低压二极管,以减小二极管结电容 Cj。

2)引入箝位回路旁路干扰电流。

3)在 dv/dt 的干扰回路中加入阻尼电阻(阻值小,几欧即可),如图 3 中 R2。

4)在版图设计时,应缩短保护回路的走线,减少寄生电感。

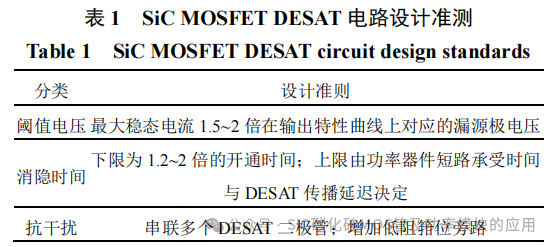

综上所述,将 DESAT 应用于 SiC MOSFET 短路保护中,需从 SiC MOSFET 的短路特性和开关特性出发,结合工程应用的可操作性展开设计。具体设计准则可以总结如表 1 所示。

2 基于 GaN 的 DESAT 电路的研究

由于 SiC MOSFET 的短路耐受时间远低于IGBT 器件,DESAT 电路的低传输延时和高速响应是保障 SiC MOSFET 在短路故障下安全可靠关断的重要参数。本章节将展开基于 GaN 的电压源DESAT 电路的设计,以实现低传输延时、低损耗和小型化。该电路可以配合商用 SiC MOSFET 的驱动芯片使用,也可以配合独立驱动级使用,如本文中使用的谐振驱动。

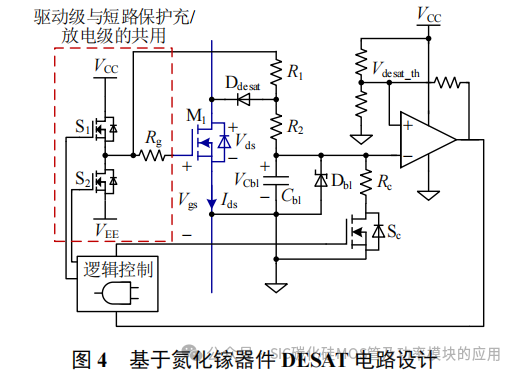

2.1 电路设计

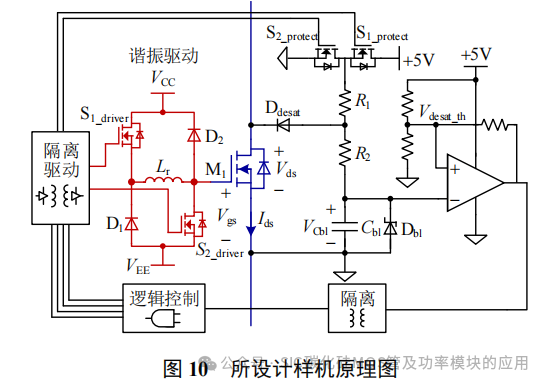

本文所提出的基于 GaN 器件的电压源型DESAT 电路如下图 4 所示。采用 GaN HEMT(S1 和S2)构建半桥放大电路,既作为 SiC MOSFET(M1)的驱动电路,也作为 DESAT 电路的充放电电路。Cbl为采样电容,R1 用于降低 DESAT 电路的静态损耗,R2 用于增强抗干扰能力。消隐时间由 Cbl、R1、R2所组成的 RC 网络决定。稳压二极管 Dbl 用于防止采样电容电压过高损坏采样电容及比较器。阈值电压 Vdesat_th由 Vcc与电阻分压得到。Rc和 Sc构成采样电容的快速放电支路,在器件关断时打开 Sc以抑制dv/dt 带来的干扰,其中 Sc选用相同的 GaN 器件。采用滞环比较器避免干扰对于保护信号的影响。

2.2 低压 GaN 器件的优势

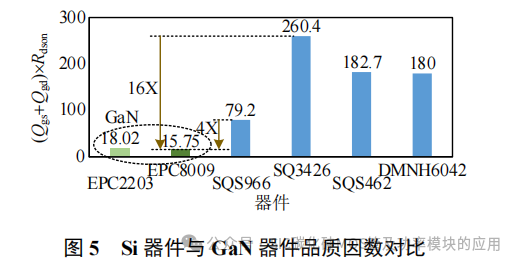

GaN 晶体管为宽禁带半导体功率器件的典型代表,具有更快的电子饱和速率、极低的栅极电荷和寄生电容。因采用球栅阵列封装(ball gridarray,BGA)低压 GaN 器件的尺寸很小。以 GaN EPC8009(65V Id 4A)器件和硅 SQS966(60VId 6A)为例,EPC8009 的尺寸仅为 SQS966 的 32%。

功率器件的品质因素(Qg Rdson)决定其驱动速度和导通损耗。如图 5 所示,与相似电压和电流等级的硅器件相比,GaN 器件的品质因数比硅器件要低 4倍以上,具有更快的驱动速度和更低的导通损耗。

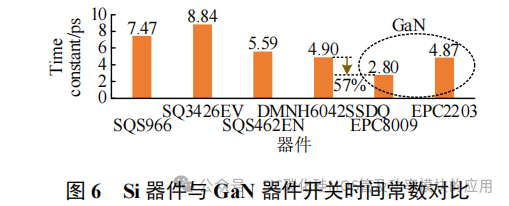

功率器件输出电容的充–放电时间直接决定器件的开关延时和开关损耗。因而,定义器件开关时间常数Coss Rdson来评估DESAT电路中功率器件的延时和损耗特性。图 6 为相似电压和电流等级的硅和 GaN 器件的开关时间常数对比。由于器件输出电容呈非线性特性,采用电荷等效法提取等效输出电容(Coss_eqv),即:

如图 6 所示,时间常数最低的 Si 器件仍比 GaN晶体管高 57%。GaN 器件具有更快的开关速度和更低的开关延时。

由此可见,低压 GaN 器件具有开关速度快、开关延时低、开关和导通损耗低、易驱动、体积小等优势。SiC MOSFET 短路保护要求纳秒级的 DESAT电路的动作速度,以实现 SiC MOSFET 的安全关断。采用 GaN 器件的电压源 DESAT 电路,不仅降低 DESAT 传播延时,提升动作速度,也可降低DESAT 电路的损耗,更加有利用与系统集成。

2.3 仿真验证

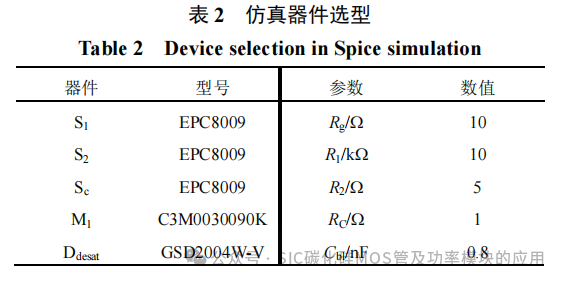

采用 LTSPICE 对基于 GaN 器件的电压源DESAT 保护电路进行仿真。如下表 2 所示,功率器件 M1 采用 CREE 公司的 900V/63A SiC MOSFET,型号为 C3M0030090K。开关器件 S1、S2、Sc 使用 EPC 公司 65V/4A EPC8009 GaN HEMT。仿真中母线电压为 500V,Ddesat 使用两个 300V 肖特基二极管串联,型号为 GSD2004W。

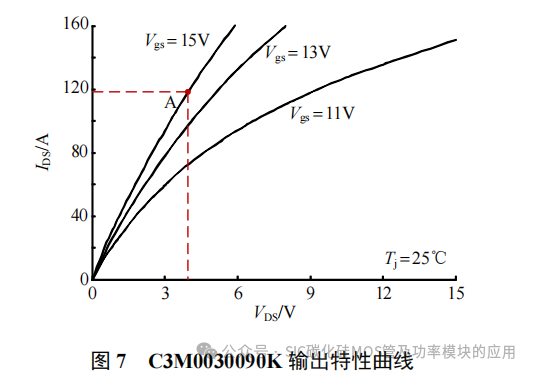

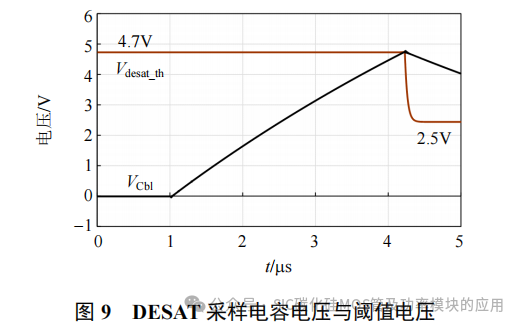

短路阈值电压的选取依据 C3M0030090K 在两倍的最大稳态电流下所对应的漏源级电压。假设器件结温为 25℃,栅极驱动电压为 15V,两倍的最大稳态电流为 126A,即图 7 中 A 点,因而可得到相应的漏源级电压 Vds_th为 4.3V。

考虑到 Ddesat正向导通压降约为 0.4V,故将短路阈值电压 Vdesat_th,即比较器参考电压设为 4.7V。依据式(6),设定 50%的时间裕量,选取器件短路承受时为 10s,将消隐时间设为 3s。依据式(2),可计算得到 Cbl 0.8nF,R1 10k,R2 5。

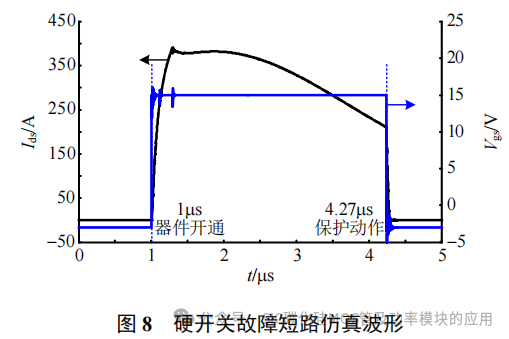

如图 8 所示,SiC MOSFET 在 1s 处发生硬开关故障,DESAT 保护电路经过 3.27s 对 Cbl 进行充电,并在 4.27s 时触发保护动作。图 9 为 SiC 短路故障下,DESAT 采样电容电压和阈值电压的变化情况。

DESAT 电路传播延时包括比较时间,逻辑动作时间,以及驱动动作时间。由于仿真中比较器、逻辑门等均为理想器件,故仿真中 DESAT 电路的传播延时仅由 GaN 的开关时间所决定。GaN 的驱动动作时间为 14.1ns。若使用相同电压,电流等级的Si MOSFET 器件(ROHM SP8K32 60V/4.5A)作为驱动半桥,DESAT 电路的驱动动作时间为 60.7ns。由此可见,使用 GaN HEMT EPC8009 的 DESAT 电路动作时间仅为 Si MOSFET SP8K33 的 DESAT 动作时间的 23.2%。

2.4 样机设计与验证

为了验证基于 GaN 的电压源 DESAT 电路特性,搭建相应样机并配合已有基于 GaN 的谐振驱动展开验证,实验样机的原理图如图 10 所示。其中 GaN 谐振驱动由 S1_driver、S2_driver、D1、D2、Lr构成。Lr与 M1 的栅–源极电容 Ciss 构成谐振回路。在谐振开通时,导通 S1_driver导通,驱动电源 VCC通过 Lr对 M1 进行谐振开通,S1_driver开通时长为 Lr和Ciss 的 1/4 谐振周期;M1关断时通过 S2_driver进行直接箝位关断,不仅关断速度快也可有效抑制串扰问题。谐振驱动因更快的驱动时间和更小的驱动损耗,是 SiC 高频工作时的更好选择。

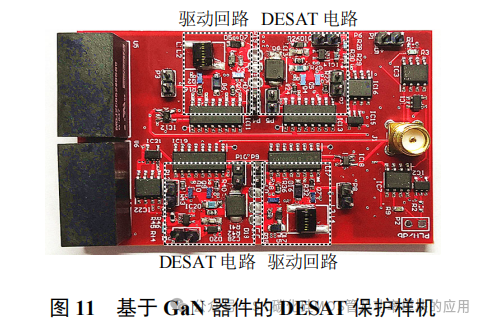

实验原型机如图 11 所示,其中功率开关器件S1_protect、S2_protect、S1_driver、S2_driver均选用 EPC 公司65V/4A GaN HEMT,型号为 EPC8009。采用 SiliconLabs 的 Si8273 作为 GaN 器件的隔离驱动,驱动芯片的传播延时为 30ns。谐振驱动中谐振电感 Lr使用Coilcraft 公司 100nH 空心电感(1812SMS-R10)。

Ddesat 使用 1200V(GB01SLT12)SiC 肖特基二极管与40V(RB168MM-40)肖特基二极管的串联。DESAT电路中比较器使用 TI 公司的 TLV3201,该比较器响应速度快,传播延时仅 40ns。所设计的电压源 DESAT 电路尺寸(蓝色框内电路)为 1.6cm 1.3cm。样机设计中,选取 1.5 倍的最大稳态电流作为短路电流阈值。根据 SiC C3M0030090K 器件数据手册,可得到相应的漏源级电压 Vds_sc为 3V。考虑Ddesat 正向导通压降约为 0.2V,故将短路阈值电压Vdesat_th 设为 3.2V。

DESAT 保护电路的信号控制需与谐振驱动信号相配合,即在谐振开通过程结束后,开通 S1_protect对采样电容进行充电。该控制策略有效避免了 SiC器件开通过程中采样电容的充电,因此 DESAT 电路可采用更短的消隐时间或更小的采样电容。S2_driver 导通以实现功率器件的箝位关断,同时S2_protect 导通对采样电容进行放电。谐振驱动(S1_driver,S2_driver)与 DESAT 保护电路(S1_protect,S2_protect)在正常工作时的控制信号如图 12 所示。

首先,采用单脉冲工作模式验证基于 GaN 器件的 DESAT 电路的基本性能。

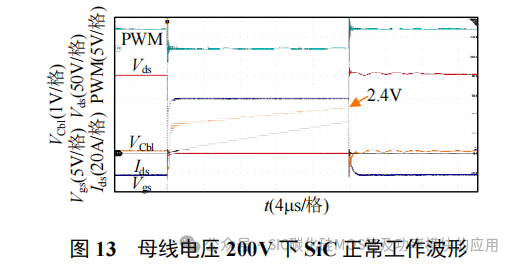

图 13 为 SiC 器件正常工作下脉宽调制(pulse width modulation,PWM)输入、门级驱动以及 DESAT 采样电容的波形。由于Ddesat 的持续导通,Cbl 两端电压随着电路中电感电流的增加而增加。在脉冲结束时,Cbl 两端电压为2.4V,未超过所设置的 Vdesat_th 阈值电压,没有触发短路保护。当 VCbl 达到 Vdesat_th 时,DESAT 电路将触发短路保护。SiC 器件的过流保护和短路保护,在 DESAT 电路的短路保护触发的原理上具有相似性。本文基于本实验的双脉冲平台,验证 SiC 器件过流保护下基于 GaN 的电压源 DESAT 电路的动态特性。

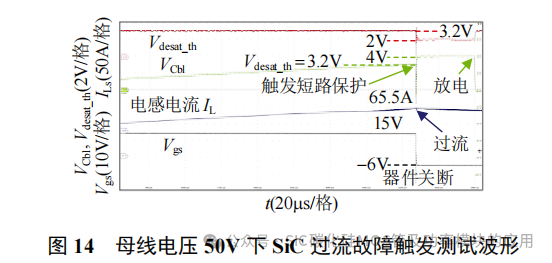

图 14 展示了 DESAT 电路的短路故障触发时的主要工作波形。电路中母线电压为 50V,且 Vdesat_th为 3.2V。当 VCbl 高于 Vdesat_th 时,比较器输出将跳变为低电平。S2_driver导通,功率器件的驱动信号 Vgs从 15V 降至5V,功率器件关断,电感电流不再上升。由于设计了滞环网络,在比较器输出从高到低跳变后,Vdesat_th 将从 3.2V 下降至 2V。当 VCbl 下降至 0V,Vdesat_th 则通过滞环网络复位至 3.2V。

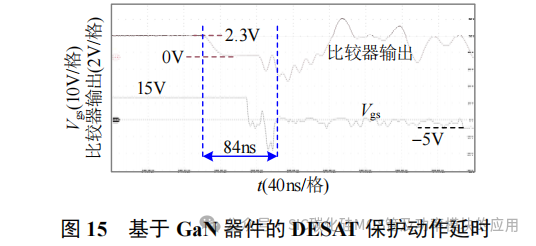

如图 15 所示,从 DESAT 比较器输出低电平到功率器件关断,延时为 84ns,其中包括了逻辑动作时间和驱动切换时间。考虑到所用比较器传播延时为 40ns,因而所设计的 GaN 电压源 DESAT 保护总传播延时为 124ns。

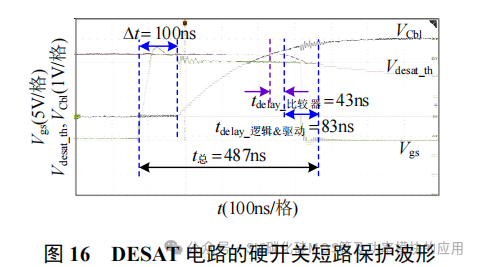

图 16 体现了基于 GaN 器件的 DESAT 电路在硬开关故障下的关键波形。S1_driver关断后,S1_protect打开为 Cbl充电。Cbl充电 261ns 后,VCbl达到 Vdesat_th,再经过 43ns 后比较器输出跳变为低电平,Vdesat_th由于滞环设计下降。经过 83ns 的动作延时,Vgs降低为5V,功率器件关断。

综上,实验可较为充分验证基于 GaN 器件的DESAT 电路的基本性能和高速的响应速率。另一方面,GaN 器件体积小,且器件损耗与驱动所需能量远低于低压硅器件,可实现 DESAT 电路的低损耗和高功率密度集成。

3 结论

本文对 DESAT 电路应用于 SiC MOSFET 短路保护中的关键问题与参数设计进行了深入讨论,总结出 DESAT 电路的设计准则:

1)设定合理的短路电流并结合在 SiC MOSFET I–V 输出特性曲线得到阈值电压,可在有效保护功率器件的同时避免出现过保护问题;

2)消隐时间的设计应基于 SiC MOSFET 短路承受时间,结合 DESAT 电路的传播延时,确保足够的裕量;

3)为防止器件 dv/dt 串扰对 DESAT 产生干扰,应降低 DESAT 电路中二极管Ddesat 结电容,并加入阻尼电阻与低阻箝位支路。

在此基础上,本文提出基于 GaN 器件的 DESAT 保护电路。由于低压 GaN 器件具有体积小,寄生参数小,开关速度快等特性,基于 GaN 器件 DESAT 电路相比基于硅器件的 DESAT 电路在体积、损耗和响应时间上更具优势。GaN DESAT 电路驱动动作时间仅为 Si DESAT 电路的 23.2%,大大降低了DESAT 电路的传播延时,提升 SiC MOSFET 短路保护速度。

声明:此文来源网络,是出于传递更多信息之目的,文中观点仅供分享交流,不代表本公众号立场。转载请注明出处,若有来源标注错误或如涉及版权等问题,请与我们联系,我们将及时更正、删除,谢谢。

很厉害